Manonmaniam Sundaranar University, Directorate of Distance & Continuing Education, Tirunelveli - 627 012 Tamilnadu, India

# **OPEN AND DISTANCE LEARNING (ODL) PROGRAMMES**

(FOR THOSE WHO JOINED THE PROGRAMMES FROM THE ACADEMIC YEAR 2023–2024)

# I M.Sc. Physics

# LINEAR AND DIGITAL ICs AND APPLICATIONS

# **Course Material**

Prepared

By

Dr. V. Sabarinathan

Dr. S. Arunavathi

Assistant Professor

# **Department of Physics**

**Manonmaniam Sundaranar University**

# Tirunelveli - 12

LINEAR AND DIGITAL ICS AND APPLICATIONS

1

# LINEAR AND DIGITAL ICs AND APPLICATIONS

#### UNIT I:

# INTEGRATED CIRCUITS AND OPERATION AMPLIFIER

Introduction, Classification of IC's, basic information of Op-Amp 741 and its features, the ideal Operational amplifier, Op-Amp internal circuit diagram, Op-Amp. Characteristics, DC and AC performance Characteristics

## UNIT II:

# **APPLICATIONS OF OP-AMP**

LINEAR APPLICATIONS OF OP-AMP: Solution to simultaneous equations and differential equations, Instrumentation amplifiers, V to I and I to V converters

NON - LINEAR APPLICATIONS OF OP-AMP: Sample and Hold circuit, Log and Antilog amplifier, multiplier and divider Comparators, Schmit trigger, Multivibrators, Triangular and Square waveform generators

# **UNIT III**

#### **ACTIVE FILTERS & TIMERAND PHASE LOCKED LOOPS**

ACTIVEFILTERS: Introduction, Butter worth filters-1<sup>st</sup> order, 2<sup>nd</sup> order low and high pass filters, band pass, band reject and all pass filters.

TIMER AND PHASE LOCKED LOOPS :Introduction to IC 555timer description of functional diagram, mono stable and astable operations and applications, Schmitt trigger, PLLintroduction, basic principle, phase detector /comparator, voltage controlled oscillator (IC566), low pass filter monolithic PLL and applications of PLL

#### **UNIT IV:**

# **VOLTAGE REGULATOR & D to A AND A to D CONVERTERS**

**VOLTAG EREGULATOR:** Introduction, Series Op-Amp regulator, IC Voltage Regulators, IC 723 general purpose regulators, Switching Regulator.

2

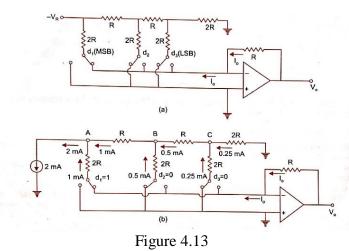

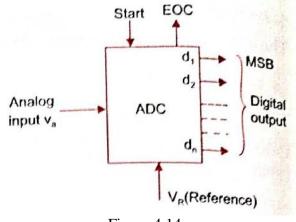

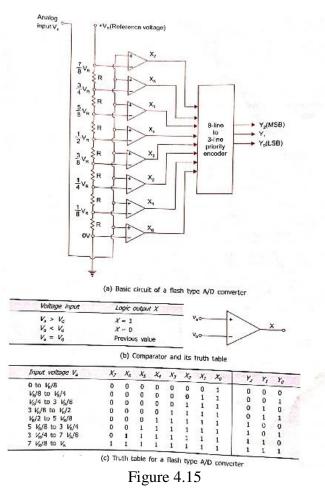

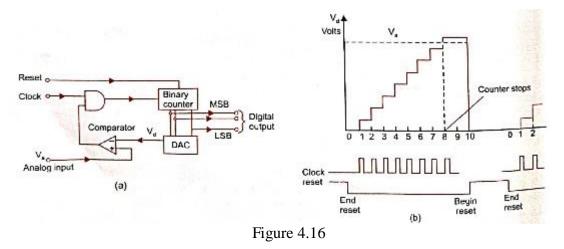

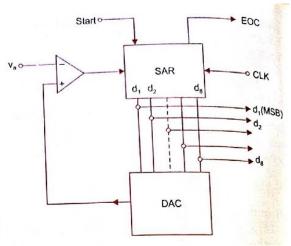

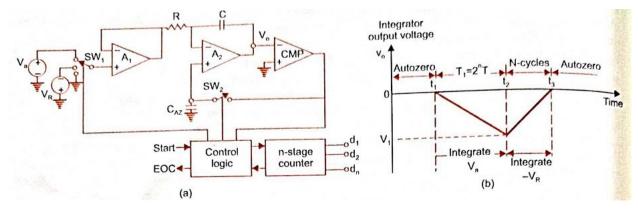

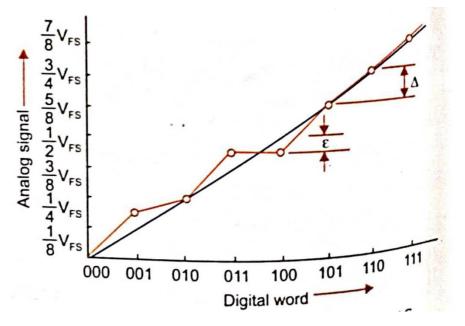

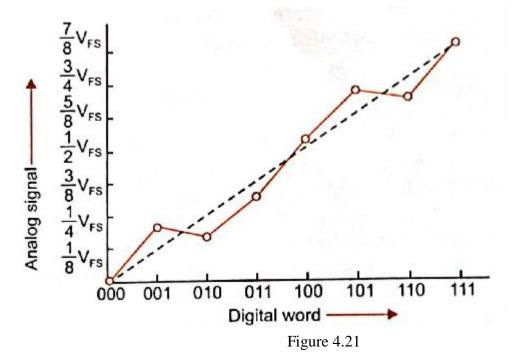

**D** to A AND A to D CONVERTERS : Introduction, basic DAC techniques – weighted resistor DAC, R-2R ladder DAC ,inverted R-2R DAC, A to D converters-parallel comparator type ADC, counter type ADC ,successive approximation ADC and dual slope ADC, DAC and ADC Specification

# UNIT V:

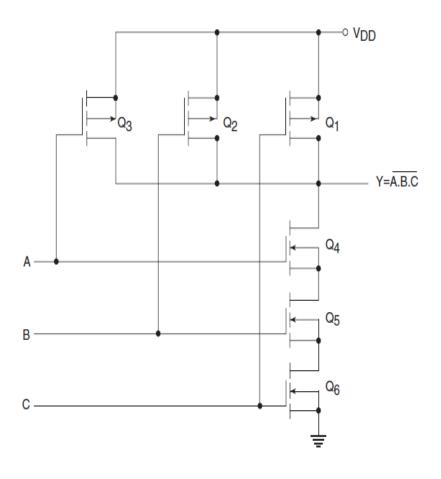

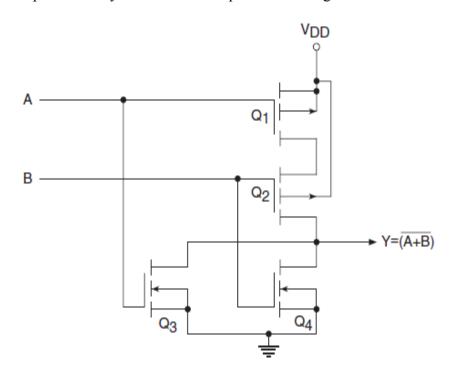

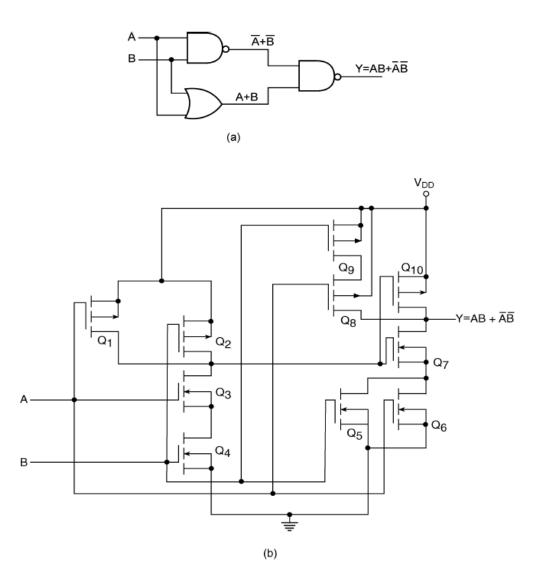

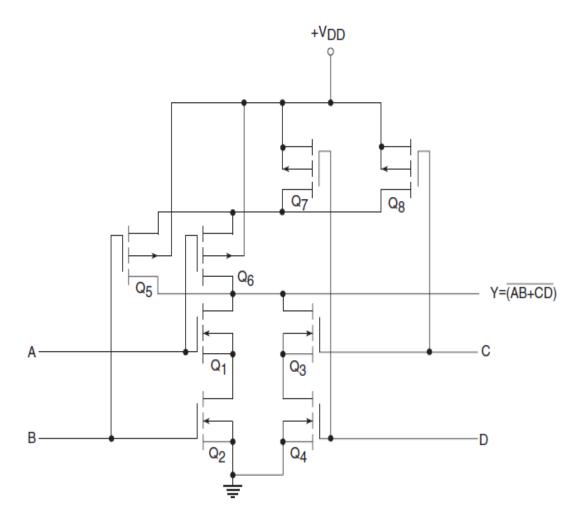

CMOS LOGIC, COMBINATIONAL CIRCUITS USING TTL 74XX ICs & SEQUENTIAL CIRCUITS USING TTL 74XX ICs

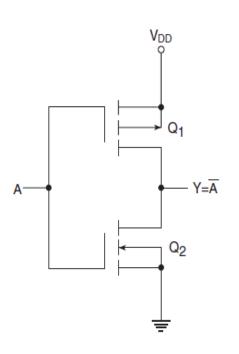

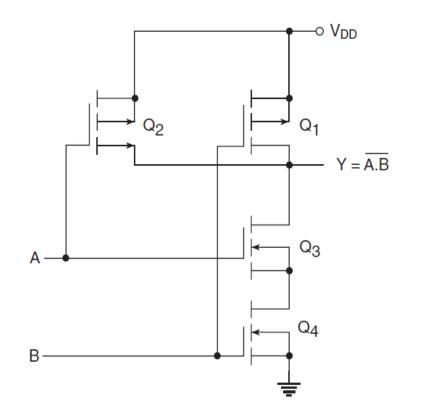

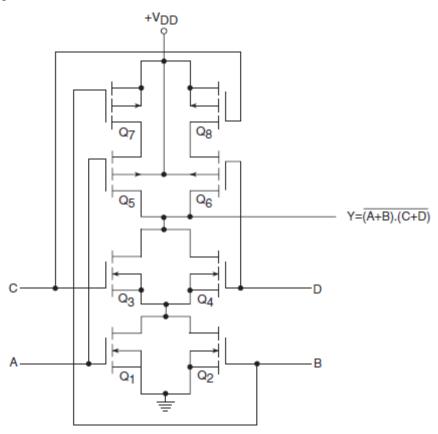

**CMOS LOGIC** : CMOS logic levels, MOS transistors, Basic CMOS Inverter, NAND and NOR gates, CMOS AND – OR – INVERT and OR- AND - INVERT gates, implementation of any function using CMOS logic.

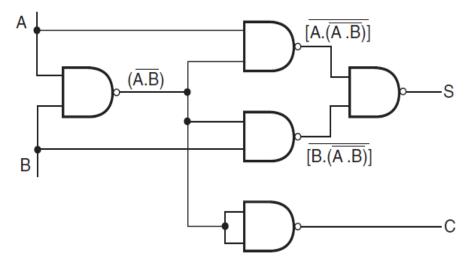

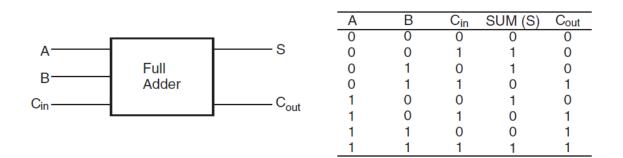

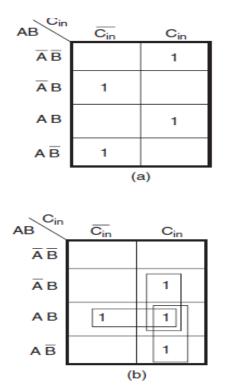

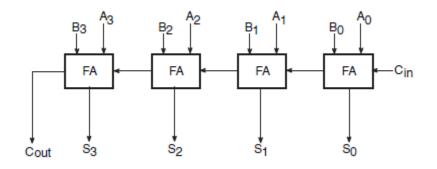

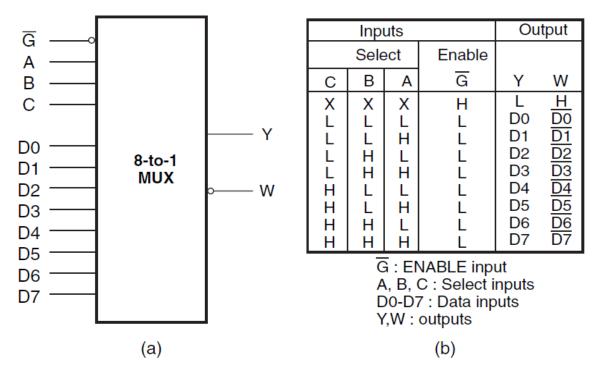

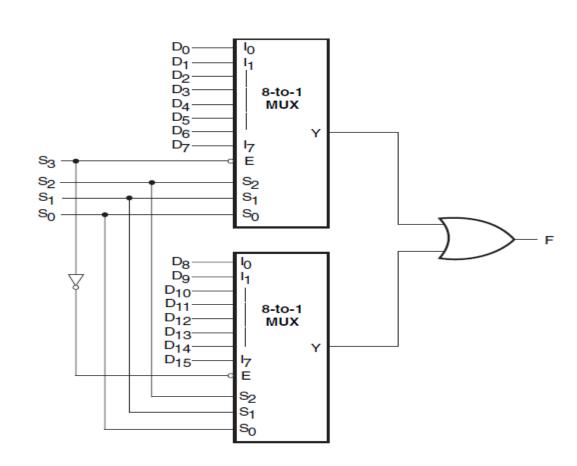

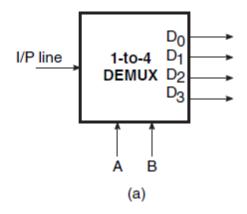

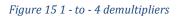

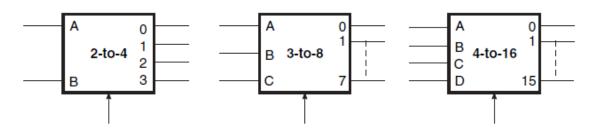

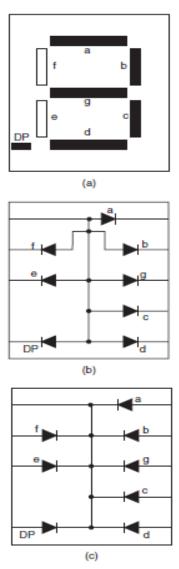

**COMBINATIONAL CIRCUITS USING TTL 74XX ICs**: Study of logic gates using 74XX ICs, Four-bit parallel adder (IC7483),Comparator (IC 7485), Decoder (IC 74138, IC 74154), BCD to 7-segment decoder (IC7447), Encoder (IC74147), Multiplexer(IC74151), Demultiplexer (IC74154).

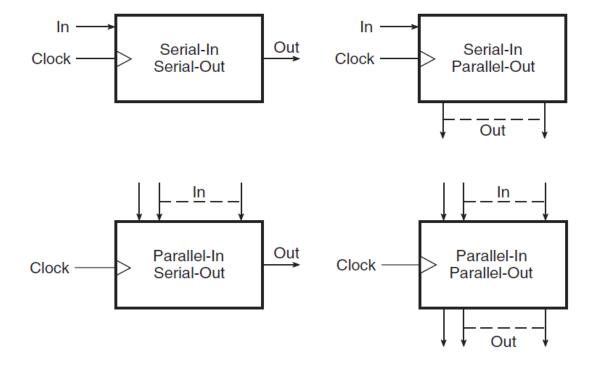

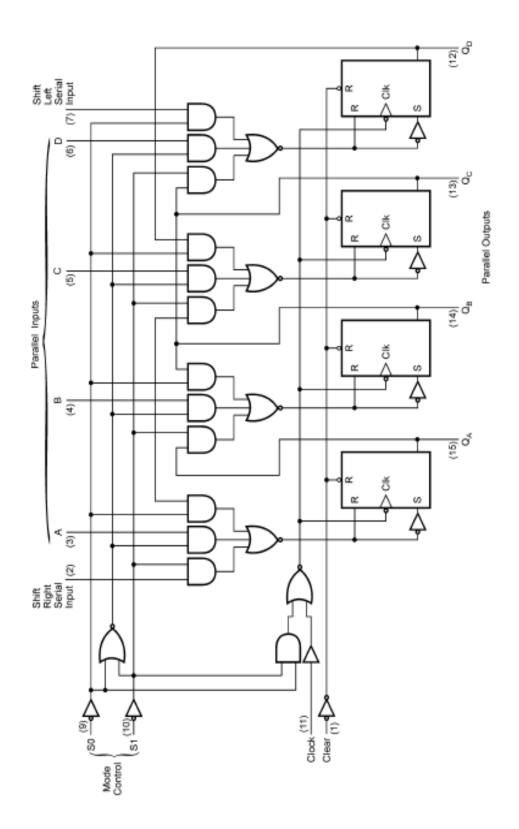

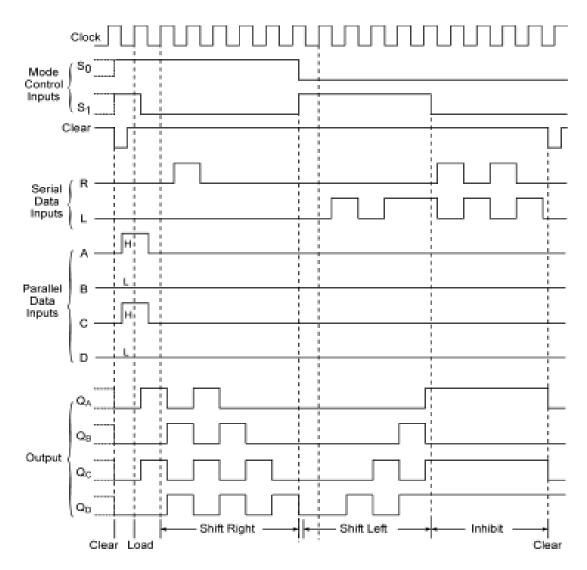

**SEQUENTIAL CIRCUITS USING TTL 74XX ICs**: Flip Flops (IC7474, IC7473), Shift Registers, Universal Shift Register (IC74194), 4-bit asynchronous binary counter (IC7493).

# UNIT I

# INTEGRATED CIRCUITS AND OPERATIONAL AMPLIFIER

Introduction, Classification of IC's, basic information of Op-Amp 741 and its features, the ideal Operational amplifier, Op-Amp internal circuit and Op-Amp. Characteristics

# **1.1 Introduction**

The integrated circuit or IC is a miniature, low cost electronic circuit consisting of active and passive components that are irreparably joined together on a single crystal chip of silicon. Most of the components used in ICs are not similar to conventional components in appearance although they perform similar electrical functions.

These circuits naturally offer a number of distinct advantages over those made by interconnecting discrete components. These may be listed as follows:

1. Miniaturization and hence increased equipment density

- 2. Cost reduction due to batch processing

- 3. Increased system reliability due to elimination of soldered joints

4. Improved functional performance (as it is possible to fabricate even complex circuits for better characteristics)

5. Matched devices

6. Increased operating speeds (due to the absence of parasitic capacitance effect)

7. Reduction in power consumption.

# **1.2** Classification of IC's

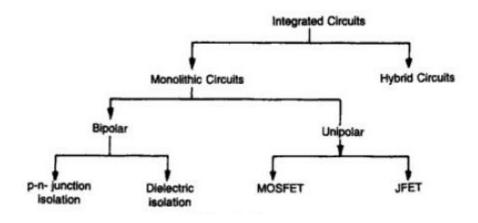

Integrated circuits offer a wide range of applications and could be broadly classified as:

- Digital ICs

- Linear ICs

Based upon the above requirements, two distinctly different IC technologies namely, Monolithic technology and Hybrid technology have been developed.

In monolithic integrated circuits, all circuit components, both active and passive elements and their interconnections are manufactured into or on top of a single chip of silicon. The monolithic circuit is ideal for applications where identical circuits are required in very large quantities and hence provides lowest per-unit cost and highest order of reliability. In hybrid circuits, separate component parts are attached to a ceramic substrate and interconnected by means of either metallization pattern or wire bonds.

1.3 Basic Information of op – amplifier 741 and its features

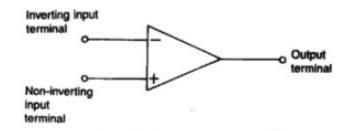

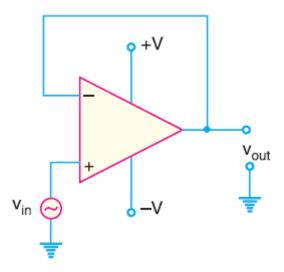

The circuit schematic of an op-amp is a triangle as shown in Fig. 1.1. It has two input terminals and one output terminal. The terminal with a (-) sign is called inverting input terminal and the terminal with (+) sign is called the non-inverting input terminal.

Figure 1.1

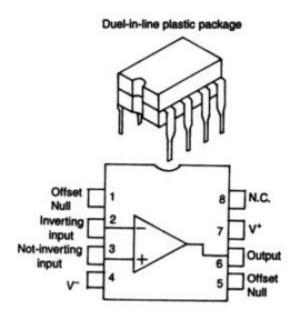

Op-amps have five basic terminals, that is, two input terminals, one output terminal and two power supply terminals. The significance of other terminals varies with the type of the op-amp. In case of DIP package of 741 shown in figure 1.2, the top pin on the left of the notch locates pin 1, has a dot on it for identification. The other pins are numbered counter-clockwise from pin 1. Pin 2 is called the inverting input terminal and pin 3 is the non-inverting input terminal, pin 6 is the output terminal and pins 7 and 4 are the power supply terminals labelled as V and V-respectively. Terminals 1 and 5 are used for de offset. The pin 8 marked NC indicates No Connection.

Figure 1.2 pin configuration of 8-pin DIP IC 741

#### 1.4 The Ideal Operational amplifier

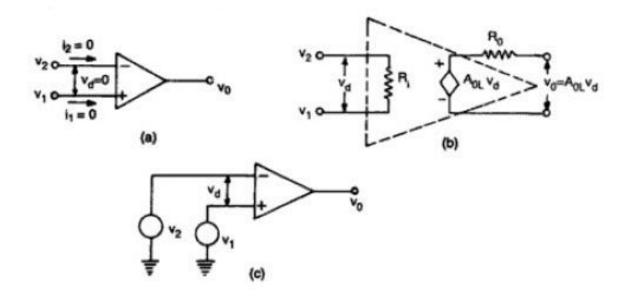

The schematic symbol of an op-amp is shown in Fig.1.3(a) It has two input terminals and one output terminal. Other terminals have not been shown for simplicity. The and + symbols at the input refer to inverting and non-inverting input terminals respectively, i.e if u1 = 0, output v is 180° out of phase with input signal ug. And, when v2 = 0, output v, will be in phase with the input signal applied at v1. This op-amp is said to be ideal if it has the following characteristics.

Open loop voltage gain,  $A_{OL} = \infty$

LINEAR AND DIGITAL ICs AND APPLICATIONS

Input impedance,  $R1 = \infty$

Output impedance,  $R_{o=0}$

Bandwidth ,BW =  $\infty$

Zero offset, i.e.  $v_0 = 0$  when  $V_1 = V_2 = 0$ .

Figure 1.3

It can be seen that

(i) an ideal op-amp draws no current at both the input terminals i.e., i=0. Because of infinite input impedance, any signal source can drive it and there is no loading on the preceding driver stage.

(ii) Since gain is  $\infty$ , the voltage between the inverting and non- inverting terminals, i.e., differential input voltage  $V_a = (V_1 - V_2)$  is essentially zero for finite output voltage  $v_0$

7

(iii) The output voltage  $v_0$ , is independent of the current drawn from the output as R = 0. The output thus can drive an infinite number of other devices.

The above properties can never be realized in practice. However, the use of such an Ideal op-amp model simplifies the mathematics involved in op-amp circuits. There are practical op-amps that can be made to approximate some of these characteristics.

A physical amplifier is not an ideal one. So, the equivalent circuit of an op-amp may be shown in Fig. 1.3 (b) .

#### 1.4.1 Open loop operation of op-amp 741

The simplest way to use an op-amp is in the open loop mode. Refer to Fig. 1.3 (c). The output assumes one of the two possible output states, that is, +Vsat or -Vsat and the amplifier acts as a switch only. This has a limited number of applications such as voltage comparator, zero crossing detector etc.

#### 1.4.2 Feedback in op-amp

The utility of an op-amp can be greatly increased by providing negative feedback. The output in this case is not driven into saturation and the circuit behaves in a linear manner.

#### Two Important Negative Feedback Circuits

There are two basic feedback connections used. In order to understand the operation of these circuits, we make two realistic simplifying assumptions discussed earlier also.

- The current drawn by either of the input terminals (non-inverting and inverting) is negligible.

- The differential input voltage v<sub>a</sub> between non-inverting and inverting input terminals is essentially zero.

#### **1.4.3 Inverting Amplifier :**

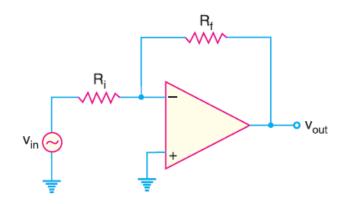

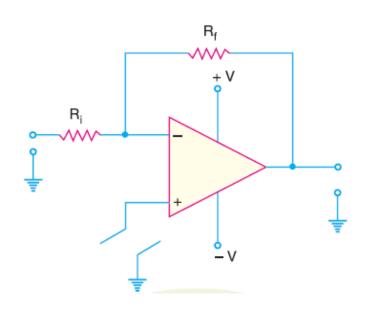

An *OP* amplifier can be operated as an inverting amplifier as shown in Fig. 1.4. An input signal  $v_{in}$  is applied through input resistor *Ri* to the minus input (inverting input). The output is fed back to the same minus input through feedback resistor *Rf*. The plus input (noninverting input) is grounded. Note that the resistor *Rf* provides the *negative feedback*. Since the input signal is applied to the inverting input (–), the output will be inverted (*i.e.* 180° out of phase) as compared to the input. Hence the name inverting amplifier.

Figure 1.4

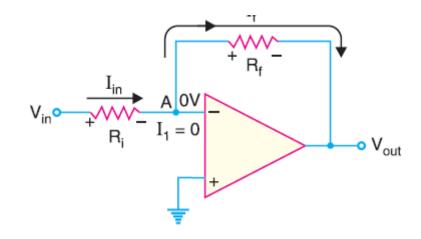

**Voltage gain:** An OP-amp has an infinite input impedance. This means that there is zero current at the inverting input. If there is zero current through the input impedance, then there must be *no* voltage drop between the inverting and non inverting inputs. This means that voltage at the inverting input (–) is zero (point *A*) because the other input (+) is grounded. The 0V at the inverting input terminal (point *A*) is referred to as **virtual ground.** This condition is illustrated in Fig.1.5. The point *A* is said to be at virtual ground because it is at 0V but is not physically connected to the ground (*i.e.* VA = 0V).

Figure 1.5

the current  $I_{in}$ , the inverting input is zero. Therefore, current  $I_{in}$  flowing through Ri entirely flows through feedback resistor Rf. In other words,  $I_f = I_{in}$

Now

$$I_{in} = \frac{Voltage \ across \ R_i}{R_i} = \frac{V_{in}}{R_i}$$

$$I_{f} = \frac{Voltage\ across\ R_{f}}{R_{f}} = \frac{-V_{out}}{R_{f}}$$

Since

$$I_f = I_{in}$$

,  $\frac{V_{in}}{R_i} = \frac{-V_{out}}{R_f}$

Voltage gain,

$$A_{CL} = \frac{V_{out}}{V_{in}} = -\frac{R_f}{R_i}$$

The output voltage is 180° out of phase with the input. Since the voltage drop across  $R_f$  is of the opposite polarity to the applied voltage, the circuit is providing negative feedback.

It is worthwhile to give a brief discussion about the input impedance and output impedance of inverting amplifier.

The negative sign indicates that output signal is inverted as compared to the input signal. The following points may be noted about the inverting amplifier : 10

LINEAR AND DIGITAL ICS AND APPLICATIONS

The closed-loop voltage gain  $(A_{CL})$  of an inverting amplifier is the ratio of the feedback resistance *Rf* to the input resistance *Ri*. *The closed-loop voltage gain is independent of the OP-amp's internal open-loop voltage gain*. Thus the negative feedback stabilises the voltage gain.

The inverting amplifier can be designed for unity gain. Thus if Rf = Ri, then voltage gain,  $A_{CL} = -1$ . Therefore, the circuit provides a unity voltage gain with 180° phase inversion. If Rf is some multiple of Ri, the amplifier gain is constant. For example, if Rf = 10 Ri, then  $A_{CL} = -10$  and the circuit provides a voltage gain of exactly 10 along with a 180° phase inversion from the input signal. If we select precise resistor values for Rf and Ri, we can obtain a wide range of voltage gains. *Thus the inverting amplifier provides constant voltage gain*.

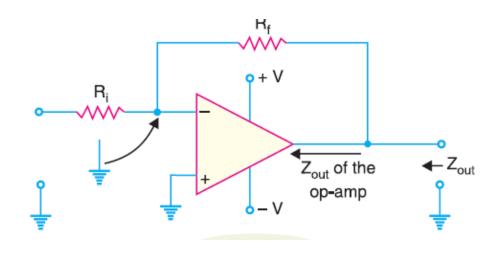

(*i*) **Input impedance.** While an *OP*-amp has an extremely high input impedance, the inverting amplifier does not. As this figure 1.6 shows, the voltage source "sees" an input resistance (Ri) that is going to virtual ground. Thus the input impedance for the inverting amplifier is

# Zi ~Ri.

The value of *Ri* will always be much less than the input impedance of the *OP*amp. Therefore, the overall input impedance of an inverting amplifier will also be much lower than the *OP*-amp input impedance.

(*ii*) **Output impedance.** Fig. 1.6 shows the inverting amplifier circuit. You can see from this figure that the output impedance of the inverting amplifier is the parallel combination of Rf and the output impedance of OP-amp itself. The presence of the negative feedback circuit reduces the output impedance of the amplifier to a value that is less than the output impedance of OP-amp.

11

Figure 1.6

## 1.4.4 Non-inverting amplifier

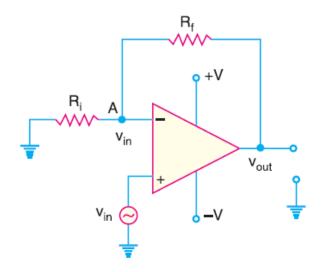

There are times when we wish to have an output signal of the same polarity as the input signal. In this case, the *OP*-amp is connected as non inverting amplifier as shown in Fig. 1.7. The input signal is applied to the non inverting input (+). The output is applied back to the input through the feedback circuit formed by feedback resistor *Rf* and input resistance *Ri*. Note that resistors *Rf* and *Ri* form a voltage divide at the inverting input (–).This produces \**negative feedback* in the circuit. Note that *Ri* is grounded. Since the input signal is applied to the non inverting input (+), the output signal will be non inverted i.e., the output signal will be in phase with the input signal. Hence, the name non-inverting amplifier.

12

Voltage gain. If we assume that we are not at saturation, the potential at point A is the same as

*Vin.* Since the input impedance of *OP*-amp is very high, all of the current that flows through *Rf* also flows through *Ri*. Keeping these things in mind, we have,

Voltage across  $R_i = V_{in} - 0$ ; Voltage across  $R_f = V_{out} - V_{in}$

Now, Current through  $R_i$  = Current through  $R_f$

$\frac{V_{in}-0}{R_i} = \frac{V_{out}-V_{in}}{R_f}$

$\frac{V_{out}}{V_{in}} = 1 + \frac{R_f}{R_i}$

Voltage gain,  $A_{CL} = \frac{V_{out}}{V_{in}} = 1 + \frac{R_f}{R_i}$

The following points may be noted about the noninverting amplifier:

$A_{CL} = \frac{V_{out}}{V_{in}} = 1 + \frac{R_f}{R_i}$ , The voltage gain of noninverting amplifier also depends upon the values of *Rf* and *Ri*.

The voltage gain of a non inverting amplifier can be made equal to or greater than 1.

The voltage gain of a non inverting amplifier will always be greater than the gain of an equivalent inverting amplifier by a value of 1. If an inverting amplifier has a gain of 150, the equivalent non inverting amplifier will have a gain of 151.

The voltage gain is positive. This is not surprising because output signal is in phase with the input signal.

#### 1.4.5 Voltage follower

The voltage follower arrangement is a special case of non inverting amplifier where all of the output voltage is fed back to the inverting input as shown in Fig. 1.8. Note that we remove *Ri*

and *Rf* from the non inverting amplifier and short the output of the amplifier to the inverting input. The voltage gain for the voltage follower is calculated as given below

Figure 1.8

$$A_{CL} = 1 + \frac{R_f}{R_i} = 1 + \frac{0}{R_i} = 1$$

$(R_f = 0\Omega)$

Thus the closed-loop voltage gain of the voltage follower is 1. The most important features of the voltage follower configuration are its *very high input impedance* and its *very low output impedance*. These features make it a nearly ideal buffer amplifier to be connected between high-impedance sources and low-impedance loads.

#### **1.5 Op-Amp internal circuit**

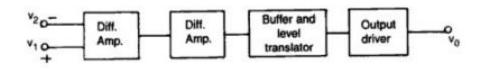

Commercial IC op-amps usually consist of four cascaded blocks as shown in Fig.1.9. The first two stages are cascaded differential amplifiers used to provide high gain and high input resistance. The third stage acts as a buffer as well as a level shifter. The buffer is usually an emitter follower whose input impedance is very high so that it prevents loading of the high gain stage. The level shifter adjusts the d.c. voltages so that output voltage is zero for zero inputs. The adjustment of d.c. level is required as the gain stages are direct coupled. As it is not possible to fabricate large value of capacitors, all ICs are direct coupled usually. The output stage is designed to provide a low output impedance as demanded by the ideal op-amp characteristics.

The output voltage should swing symmetrically with respect to ground. To allow such symmetrical swing, the amplifier is provided with both positive and negative supply voltages. Power supply voltages of + 15V are common. Additionally, an op-amp generally incorporates circuitry to provide drift compensation and frequency compensation

Figure 1.9

## **1.5.1 Differential amplifier**

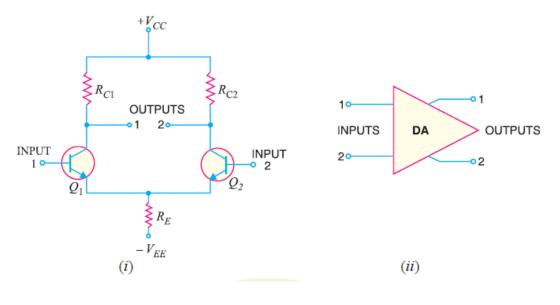

Since differential amplifier (*DA*) is key to the operation of *OP*-Amp, we shall discuss this circuit in detail. So far we have considered general-purpose amplifiers. In these conventional amplifiers, the signal (generally single input) is applied at the input terminals and amplified output is obtained at the output terminals. However, we can design an amplifier circuit that accepts two input signals and amplifies the difference between these two signals. Such an amplifier is called a *differential amplifier* (*DA*). A **differential amplifier** is a circuit that can accept two input signals and amplify the difference between these two input signals. There are two input voltages  $V_1$  and  $V_2$ . This amplifier amplifies the difference between the two input voltage signals. Therefore, the output voltage is  $V_0 = A (V_1 - V_2)$  where A is the voltage gain of the amplifier.

#### 1.5.2 Internal circuit of Differential Amplifier

The basic circuit of a differential amplifier is shown in Fig. 1.10 (*i*). It consists of two transistors Q1 and Q2 that have identical (ideally) characteristics. They share a common positive supply *VCC*, common emitter resistor *RE* and common negative supply *VEE*. Note that the circuit is symmetrical. Fig.1.10 (*ii*) shows the symbol of differential amplifier.

The following points may be noted about the differential amplifier :

(*i*) The differential amplifier (DA) is a two-input terminal device using atleast two transistors. There are two output terminals marked 1 (vout 1) and 2(vout 2).

(*ii*) The *DA* transistors Q1 and Q2 are matched so that their characteristics are the same. The collector resistors (*RC1* and *RC2*) are also equal. The equality of the matched circuit components makes the *DA* circuit arrangement completely symmetrical.

(iii) We can apply signal to a differential amplifier (DA) in the following two ways :

(a) The signal is applied to one input of *DA* and the other input is grounded. In that case, it is called *single-ended input* arrangement.

(b) The signals are applied to both inputs of *DA*. In that case, it is called *dual-ended* or *double-ended input* arrangement.

(*iv*) We can take output from *DA* in the following two ways :

(*a*) The output can be taken from one of the output terminals and the ground. In that case, it is called *single-ended output* arrangement.

(b) The output can be taken between the two output terminals (*i.e.*, between the collectors of Q1 and Q2). In that case, it is called *double-ended output* arrangement or *differential output*.

(v) Generally, the differential amplifier (DA) is operated for single-ended output. In other words, we take the output either from output terminal 1 and ground or from output terminal 2 and ground. Any input/output terminal that is grounded is at 0V.

16

LINEAR AND DIGITAL ICS AND APPLICATIONS

#### Figure 1.10

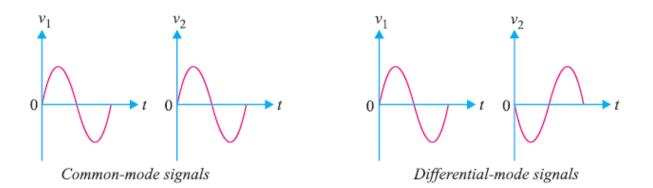

#### 1.5.3 Common-mode and Differential-mode Signals

The importance of a differential amplifier lies in the fact that the outputs are proportional to the *difference* between the two input signals. Thus the circuit can be used to amplify the difference between the two input signals or amplify only one input signal simply by grounding the other input.

The input signals to a DA are defined as :

(*i*) Common-mode signals (*ii*) Differential-mode signals

(*i*) **Common-mode signals :** When the input signals to a *DA* are in phase and exactly equal in amplitude, they are called *common-mode signals* The common-mode signals are rejected (not amplified) by the differential amplifier. It is because a differential amplifier amplifies the difference between the two signals ( $V_1 - V_2$ ) and for common-mode signals, this difference is zero. Note that for common-mode operations,  $v_1 = v_2$ .

(*ii*) **Differential-mode signals.** When the input signals to a *DA* are 180° out of phase and exactly equal in amplitude, they are called differential-mode signals. The differential-mode signals are amplified by the differential amplifier. It is because the difference in the signals is twice the value of each signal. For differential-mode signals,  $v_1 = -v_2$ .

## 1.5.4 Voltage Gains of DA

The voltage gain of a DA operating in differential mode is called differential-mode voltage gain and is denoted by  $A_{dm}$ . The voltage gain of DA operating in common-mode is called common-mode voltage gain and is denoted by  $A_{cm}$  Ideally, a DA provides a very high voltage gain for differential-mode signals and zero gain for common-mode signals. However, practically, differential amplifiers do exhibit a very small common-mode gain (usually much less than 1) while providing a high differential voltage gain (usually several thousands). The higher the differential gain w.r.t. the common-mode gain, the better the performance of the DA in terms of rejection of common-mode signals.

#### 1.5.5 Common Mode Rejection Ratio (CMRR)

A differential amplifier should have high differential voltage gain  $(A_{dm})$  and very low common mode voltage gain  $(A_{cm})$ . The ratio  $A_{dm} / A_{cm}$  is called common-mode rejection ratio *(CMRR)*

$CMRR = \frac{A_{DM}}{A_{CM}}$  Very often, the *CMRR* is expressed in decibels (*dB*). The

decibel measure for CMRR is given by;

$CMRR_{dB} = 20log_{10} CMRR$

# **1.6 Op-Amp.Characteristics**

Earlier we have used an ideal op-amp, and assumed that the op-amp responds equally well to both ac and de input voltages. However, a practical op-amp does not behave this way. A practical op-amp has some de voltage at the output even with both the inputs grounded. The factors responsible for this and the suitable compensating techniques are discussed. Also, under ac conditions the characteristics of an op-amp are frequency dependent. The limitations of an opamp under ac conditions and methods of compensation are discussed.

# **1.6.2 DC CHARACTERISTICS**

An ideal op-amp draws no current from the source and its response is also independent of temperature. However, a real op-amp does not work this way. Current is taken from the source 18 LINEAR AND DIGITAL ICS AND APPLICATIONS

into the op-amp inputs. Also the two inputs respond differently to current and voltage due to mismatch in transistors. A real op-amp also shifts its operation with temperature. These non-ideal dc characteristics that add error components to the de output voltage are:

- Input bias current

- Input offset current

- Input offset voltage

- Thermal drift.

#### **1.6.2.1 Input bias current**

The inputs to an OP- amp require some amount of d.c. biasing current for the transistors in the differential amplifier. The *input bias current* is defined as the average of the two d.c. base currents.

$$I_{in(bias)} = \frac{I_{B1} + I_{B2}}{2}$$

For example, if  $I_{Bl} = 85 \ \mu\text{A}$  and  $I_{B2} = 75 \ \mu\text{A}$ , then the input bias current is  $80\ \mu\text{A}$ . This means that when no signal is applied, the inputs of *OP*- amp (*i.e.*, *DA*) will draw a d.c. current of  $80 \ \mu\text{A}$ . The fact that both transistors in the differential amplifier require an input biasing current leads to the following operating restriction : *An OP*- *amp will not work if either of its inputs is open*. For example, look at the circuit shown in Fig. 1.11. The non-inverting input is shown to have an open between the OP- amp and ground. The open circuit would not allow the d.c. biasing current required for the operation of the differential amplifier (*The transistor associated with the inverting input would work but not the one associated with the non-inverting input)*. Since the differential amplifier would not work, the overall *OP*-amp circuit would not work. Thus an input bias current path must always be provided for *both OP*-amp inputs.

Figure 1.11

#### **1.6.2.2 Input offset current**

When the output offset voltage of a *DA* (or *OP*- amp) is eliminated, there will be a slight difference between the input currents to the non inverting and inverting inputs of the device. This slight difference in input currents is called *input offset current* and is caused by a beta ( $\beta$ ) mismatch between the transistors in the differential amplifier. As an example, suppose  $I_{B1} = 75 \ \mu$ A and  $I_{B2} = 65 \ \mu$ A. Then,  $I_{in(offset)} = 75 - 65 = 10 \ \mu$ A. The difference in the base currents indicates how closely matched the transistors are. If the transistors are identical, the input offset current is zero because both base currents will be equal. But in practice, the two transistors are different and the two base currents are not equal.

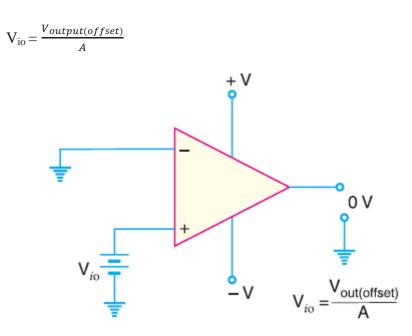

#### 1.6.2.3 Input offset voltage :

There are several methods that may be used to eliminate output offset voltage. One of these is to apply an *input offset voltage* between the input terminals of DA (or OP- amp) so as to make output 0V as shown in Fig.1.12. The value of input offset voltage (Vi0) required to eliminate the output offset voltage is given by;

20

Figure 1.12

#### 1.6.2.4 Thermal drift

Bias current, offset current and offset voltage change with temperature. A circuit carefully nulled at 25°C may not remain so when the temperature rises to 35°C. This is called drift. Often, offset current drift is expressed in nA/°C and offset voltage drift in mV/°C. These indicate the change in offset for each degree celsius change in temperature. There are very few circuit techniques that can be used to minimize the effect of drift. Careful printed circuit board layout must be used to keep op-amps away from source of heat. Forced air cooling may be used to stabilize the ambient temperature.

# **UNIT – II APPLICATIONS OF OPERATIONAL AMPLIFIERS**

LINEAR APPLICATIONS OF OP-AMP: Solution to simultaneous equations and differential equations, Instrumentation amplifiers, V to I and I to V converters.

NON-LINEAR APPLICATIONS OF OP-AMP: Sample and Hold circuit, Log and Antilog amplifier, multiplier and divider, Comparators, Schmitt trigger, Multivibrators, Triangular and Square waveform generators.

# 2.1 Linear applications of op-amp:

## 2.1.1 Solution to simultaneous equations and differential equations

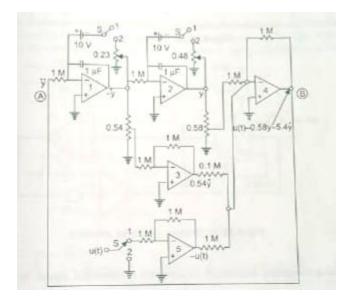

Let us now see how an analog computer can be used to solve a second order differential equation given as

$$\frac{d^2y}{dt^2} + 5.4\frac{dy}{dt} + 0.58y = u(t)$$

With initial conditions y(0) = -4.8 and  $\dot{y}(0) = 2.3$

Rewrite Equation by keeping the highest order derivative on the left hand side and taking all other terms to the right side as

$$\ddot{y} = -5.4\dot{y} - 0.58 y + u(t)$$

Assuming  $\ddot{y}$  is available, it may be successively integrated to obtain y and y as shown in Fig. 2.1 At the output of amplifier 4. i.e., point B, we obtain the sum  $-5.4\dot{y} - 0.58y+u(t)$  which is precisely equal to y with which we started . Thus points A and B may be connected together to get the computer set-up for solving the given differential equation. The initial conditions y(0)=-4.8 and  $\dot{y}(0) = 2.3$  have to be placed in the computer set-up with the V as required and potentiometer. One has to be careful about the polarity of the reference voltage for setting up the initial condition

The initial conditions are first established by putting the switch S in position 2. With S in position 1, the solution is obtained at the output terminal to which a CRO or plotter is connected.

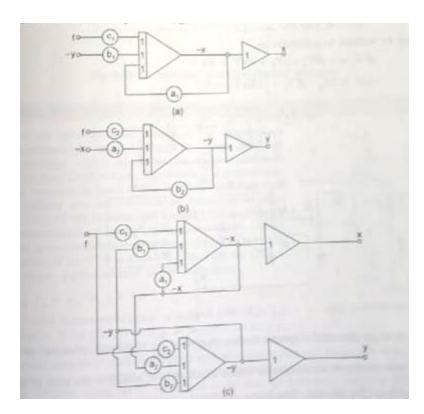

#### Solving simultaneous equations

A set of simultaneous equations in two unknowns can also be solved using analog simulation. Consider two first order differential equations:

$$\frac{dx}{dt} = -a_1x - b_1y + c_1f$$

$$\frac{dy}{dt} = -a_2x - b_2y + c_2f$$

where x and y are unknown variables. f is the input and all coefficients are known constants. Equations may be simulated separately as shown in Figs. 2.2 (a) and (b) Now interconnect the two systems to get the unknown x and y as shown in Fig.2.2 (c)

Figure 2.2

#### **2.1.2 Instrumentation Amplifiers:**

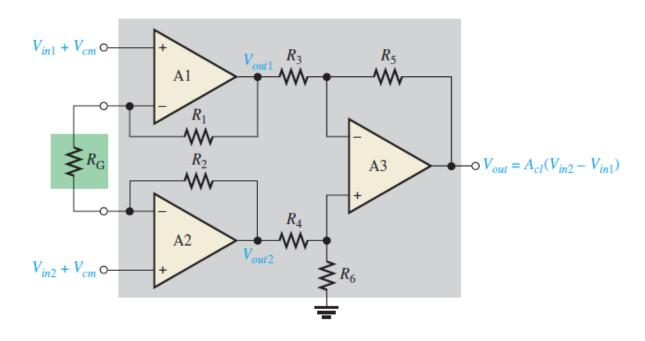

Instrumentation amplifiers are commonly used in environments with high common mode noise such as in data acquisition systems where remote sensing of input variables is required. An **instrumentation amplifier** is a differential voltage-gain device that amplifies the difference between the voltages existing at its two input terminals. The main purpose of an instrumentation amplifier is to amplify small signals that may be riding on large common mode voltages. The key characteristics are high input impedance, high common-mode rejection, low output offset, and low output impedance. The basic instrumentation amplifier is an integrated circuit that internally has three operational amplifiers and several resistors. The voltage gain is usually set with an external resistor. A basic instrumentation amplifier is shown in Figure 2.3. Op-amps A1 and A2 are non inverting configurations that provide high input impedance and voltage gain. Op-amp A3 is used as a unity-gain differential amplifier with high-precision resistors that are all equal in value (R3 = R4 = R5 = R6).

Figure 2.3

The gain-setting resistor, RG, is connected externally as shown in Figure 14–2. Op-amp A1 receives the differential input signal Vin1 on its non inverting (+) input and amplifies this signal with a voltage gain of  $A = 1 + \frac{R_1}{R_1}$

$$Av = 1 + \frac{R_1}{R_G}$$

Op-amp A1 also has *Vin*2 as an input signal to its inverting (-) input through op-amp A2 and the path formed by *R*2 and *R*G. The input signal *Vin*2 is amplified by op-amp A1 with a voltage gain of

$$Av = \frac{R_1}{R_G}$$

The overall closed-loop gain of the instrumentation amplifier is

$$Av = 1 + \frac{2R_1}{R_G}$$

LINEAR AND DIGITAL ICs AND APPLICATIONS

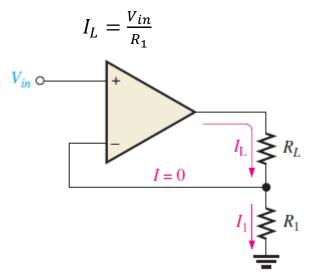

# 2.1.3 Voltage to current converters and current to voltage converters Voltage-to-Current Converter

A basic voltage-to-current converter is shown in Figure 2.4 Like the OTA, this circuit can be used in applications where it is necessary to have an output (load) current that is controlled by an input voltage. A drawback to this circuit is that the load is not grounded. Neglecting the input offset voltage, both inverting and non inverting input terminals of the op amp are at the same voltage, *Vin*. Therefore, the voltage across *R*1 equals *Vin*. Since there is negligible current at the inverting input, the current through *R*1 is the same as the current through *RL*; thus

Figure 2.4

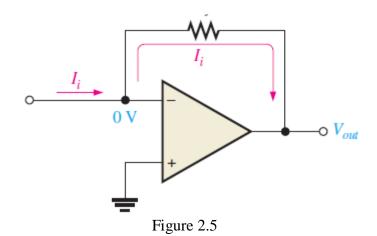

# **Current-to-Voltage Converter**

A current-to-voltage converter converts a variable input current to a proportional output voltage. A basic circuit that accomplishes this is shown in Figure 2.5. Since practically all of *Ii* is through the feedback path, the voltage dropped across Rf is I<sub>1</sub> Rf.Because the left side

of Rf is at virtual ground (0 V), the output voltage equals the voltage across Rf, which is proportional to Ii.

$$Vout = I_1 Rf$$

LINEAR AND DIGITAL ICS AND APPLICATIONS

# 2.2 Non linear Applications of Op-amp

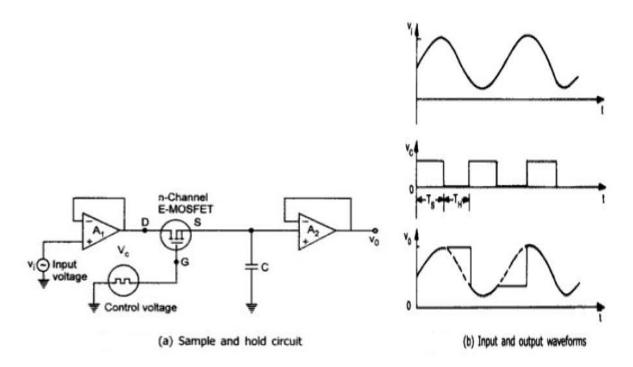

#### 2.2.1 Sample and Hold

A sample and hold circuit samples an input signal and holds on to its last sampled value until the input is sampled again. This type of circuit is very useful in digital interfacing and analog to digital and pulse code modulation systems. One of the simplest practical sample and hold circuit configuration is shown in Fig.2.5 (a). The n-channel E-MOSFET works as a switch and is controlled by the control voltage v, and the capacitor C stores the charge. The analog signal v; to be ampled is applied to the drain of E-MOSFET and the control voltage v, is applied to its gate. When v, is positive, the E-MOSFET turns on and the capacitor C charges to the instantaneous value of input v with a time constant  $[(R + r_{ps(on)})C]$  Here R, is the output resistance of the voltage follower A, and r ps(on) is the resistance of the MOSFET when on. Thus the input voltage v, appears across the capacitor C and then at the output through the voltage follower A2. The waveforms are as shown in Fig. 2.5 (b). During the time when control voltage v, is zero, the E-MOSFET is off. The capacitor C is now facing the high input impedance of the voltage follower A, and hence cannot discharge. The capacitor holds the voltage across it. The time period Tg, the time during which voltage across the capacitor is equal to input voltage is called sample period. The time period Ty of v, during which the voltage across the capacitor is held constant is called hold period. The frequency of the control voltage should be kept higher than (at least twice) the input so as to retrieve the input from output waveform. A low leakage capacitor such as Polystyrene, Mylar, or Teflon should be used to retain the stored charge

LINEAR AND DIGITAL ICs AND APPLICATIONS

Figure 2.5

# 2.2.2 Log and Antilog Amplifiers

Log amplifier

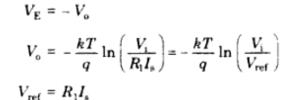

The fundamental log-amp circuit is shown in Fig. 2.6 (a) where a grounded base transistor is placed in the feedback path. Since the collector is held at virtual ground and the base is also grounded, the transistor's voltage-current relationship becomes that of a diode and is given by,

$$I_{\rm E} = I_{\rm s} \left( e^{qV_{\rm E}/kT} - 1 \right)$$

Since,  $I_{\rm C} = I_{\rm E}$  for a grounded base transistor,

$$I_{\rm C} = I_{\rm s} \left( e^{qV_{\rm g}/kT} - 1 \right)$$

$$I_{\rm s} = \text{emitter saturation current} \approx 10^{-13} \text{ A}$$

$$k = \text{Boltzmann's Constant}$$

$$T = \text{absolute temperature (in °K)}$$

Therefore,  $\frac{I_{\rm C}}{I_{\rm e}} = (e^{q V_{\rm E}/kT} - 1)$

or,

$$e^{q V_{\rm E}/kT} = \frac{I_{\rm C}}{I_{\rm s}} + 1$$

=  $\frac{I_{\rm C}}{I_{\rm s}}$  [as  $I_{\rm s} = 10^{-13}$  A,  $I_{\rm C} >> I_{\rm s}$ ]

Taking natural log on both sides, we get

$$V_{\rm E} = \frac{kT}{q} \ln\left(\frac{I_{\rm C}}{I_{\rm s}}\right)$$

Also in Fig. 2.6 (a),  $I_{\rm C} = \frac{V_{\rm i}}{R_{\rm i}}$

where

80,

The output voltage is thus proportional to the logarithm of input voltage. Although the circuit gives natural log (ln), one can find  $\log_{10}$  by proper scaling

$$\log_{10} X = 0.4343 \ln X$$

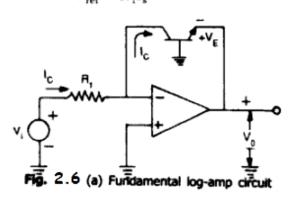

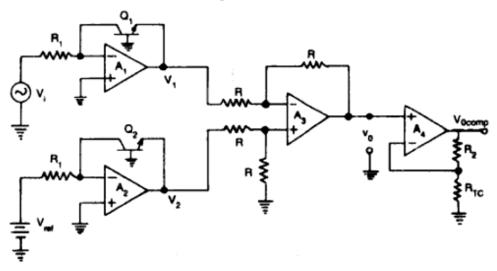

The circuit, however, has one problem. The emitter saturation current  $I_s$  varies from transistor to transistor and with temperature. Thus a stable reference voltage  $V_{ref}$  cannot be obtained. This is eliminated by the circuit given in Fig. 2.6 (b). The input is applied to one log-amp, while a reference voltage is applied to another log-amp. The two transistors are integrated close together in the same silicon wafer. This provides a close match of saturation currents and ensures good thermal tracking.

Fig. 2.6 (b) Log-amp with saturation current and temperature compensation

*'LICATIONS*

Assume,

$$I_{s1} = I_{s2} = I_s$$

and then,  $V_1 = -\frac{kT}{q} \ln\left(\frac{V_i}{R_i I_s}\right)$

and  $V_2 = -\frac{kT}{q} \ln\left(\frac{V_{ref}}{R_i I_s}\right)$

Now,  $V_o = V_2 - V_1 = \frac{kT}{q} \left[\ln\left(\frac{V_i}{R_i I_s}\right) - \ln\left(\frac{V_{ref}}{R_i I_s}\right)\right]$

or,

$$V_{\rm o} = \frac{kT}{q} \ln\left(\frac{V_{\rm i}}{V_{\rm ref}}\right)$$

Thus reference level is now set with a single external voltage source. Its dependence on device and temperature has been removed. The voltage  $V_0$  is still dependent upon temperature and is directly proportional to T. This is compensated by the last op-amp stage  $A_4$  which provides a non-inverting gain of  $(1 + R_2/R_{\rm TC})$ . Now, the output voltage is,

$$V_{o \text{ comp}} = \left(1 + \frac{R_2}{R_{\text{TC}}}\right) \frac{kT}{q} \ln\left(\frac{V_i}{V_{\text{ref}}}\right)$$

where  $R_{\rm TC}$  is a temperature-sensitive resistance with a positive coeffecient of temperature (sensistor) so that the slope of the equation becomes constant as the temperature changes.

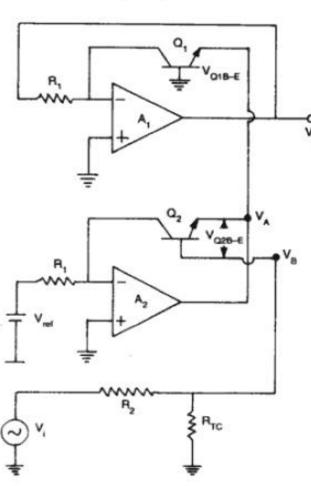

#### **Antilog amplifier**

The circuit is shown in Fig.2.7 The input  $V_i$  for the antilog-amp is fed into the temperature compensating voltage divider  $R_2$  and  $R_{\rm TC}$ and then to the base of  $Q_2$ . The output  $V_0$  of the antilog-amp is fed back to the inverting input of  $A_1$  through the resistor  $R_1$ . The base to emitter voltage of transistors  $Q_1$  and  $Q_2$  can be written as

$$V_{Q1 B-E} = \frac{kT}{q} \ln\left(\frac{V_{o}}{R_{I}I_{s}}\right)$$

$$V_{Q2 B-E} = \frac{kT}{q} \ln\left(\frac{V_{ref}}{R_{I}I_{s}}\right)$$

and

Fig. 2.7 Antilog amplifier

LINEAR AND DIGITAL ICS AND APPLICATIONS

Since the base of  $Q_1$  is tied to ground, we get

$$V_{\rm A} = -V_{\rm Q1 \ B-E} = -\frac{kT}{q} \ln\left(\frac{V_0}{R_{\rm I}I_{\rm s}}\right)$$

The base voltage  $V_{\rm B}$  of  $Q_2$  is

$$V_{\rm B} = \left(\frac{R_{\rm TC}}{R_2 + R_{\rm TC}}\right) V_{\rm i}$$

The voltage at the emitter of  $Q_2$  is

$$V_{\text{Q2 E}} = V_{\text{B}} + V_{\text{Q2 E-B}}$$

or,

$$V_{Q2 E} = \left(\frac{R_{TC}}{R_2 + R_{TC}}\right) V_i - \frac{kT}{q} \ln\left(\frac{V_{ref}}{R_1 I_s}\right)$$

But the emitter voltage of  $Q_2$  is  $V_A$ , that is,

$$V_{\rm A} = V_{\rm Q2~E}$$

or,

$$-\frac{kT}{q}\ln\frac{V_{\rm o}}{R_{\rm i}I_{\rm s}} = \frac{R_{\rm TC}}{R_{\rm 2} + R_{\rm TC}}V_{\rm i} - \frac{kT}{q}\ln\frac{V_{\rm ref}}{R_{\rm i}I_{\rm s}}$$

or,

$$\frac{R_{\rm TC}}{R_2 + R_{\rm TC}} V_{\rm i} = -\frac{kT}{q} \left( \ln \frac{V_0}{R_{\rm i} I_{\rm s}} - \ln \frac{V_{\rm ref}}{R_{\rm i} I_{\rm s}} \right)$$

or,

$$-\frac{q}{kT}\frac{R_{\rm TC}}{R_2 + R_{\rm TC}} V_{\rm i} = \ln\left(\frac{V_{\rm o}}{V_{\rm ref}}\right)$$

Changing natural log, i.e., ln to log10

$$-0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{\rm TC}}{R_2 + R_{\rm TC}}\right) V_{\rm i} = 0.4343 \times \ln\left(\frac{V_{\rm o}}{V_{\rm ref}}\right)$$

or,

$$-K'V_{\rm i} = \log_{10}\left(\frac{V_{\rm o}}{V_{\rm ref}}\right)$$

or,

$$\frac{V_0}{V_{ref}} = 10^{-K'V_i}$$

or,

$$V_{\rm o} = V_{\rm ref} (10^{-K'V_i})$$

where

by a decade.

$$K' = 0.4343 \left(\frac{q}{kT}\right) \left(\frac{R_{\rm TC}}{R_2 + R_{\rm TC}}\right)$$

Hence an increase of input by one volt causes the output to decrease

PLICATIONS

## 2.2.3 Multiplier and divider

#### Multiplier

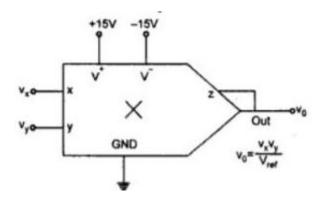

There are a number of applications of analog multiplier such as frequency doubling, frequency shifting, phase angle detection, real power computation, multiplying two signals, dividing and squaring of signals. A basic multiplier schematic symbol is shown in Fig. 2.8 (a). Two signal inputs ( $v_x$  and  $v_y$ ) are provided. The output is the product of the two inputs divided by a reference voltage  $V_{ref}$ .

Figure 2.8(a)

$$\mathbf{V}_{\mathrm{o}} = \frac{v_x \ v_y}{v_{ref}}$$

$v_x < v_{ref}$  or

$$v_y < v_{ref}$$

the output of the multiplier will not saturate. If both inputs are positive, the IC is said to be a one quadrant multiplier. A two quadrant multiplier will function properly if one input is held positive and the other is allowed to swing both positive and negative. If both inputs may be either positive or negative, the IC is called a four quadrant multiplier.

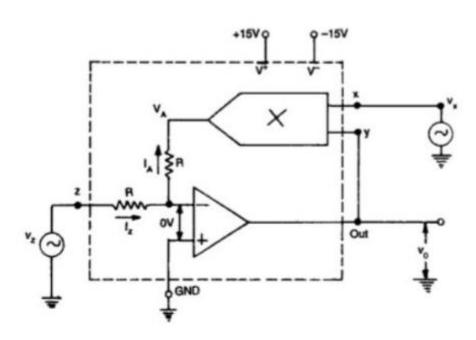

#### Divider

Division, the complement of multiplication, can be accomplished by placing the multiplier circuit element in the op-amp& feedback loop. The output voltage from the divider in Fig. 2.8(b) with input signals  $v_x$  and  $v_y$  as dividend and divisor respectively, is given by

$$\mathbf{V}_{\mathrm{o}} = - \frac{v_{ref} \ v_y}{v_x}$$

Figure 2.8(b)

Division by zero is, of course, prohibited. Multiplier IC can be used for squaring a signal. Similarly, divider circuit can be used to take the square root of a signal.

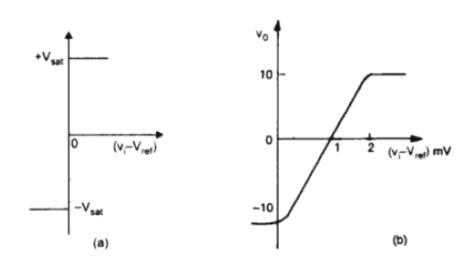

#### 2.2.4 Comparator

A comparator is a circuit which compares a signal voltage applied at one input of an opamp with a known reference voltage at the other input. It is basically an open-loop op-amp with output  $\pm$  Vsat (= Vcc) as shown in the ideal transfer characteristics of Fig.2.9 (a). However, a commercial op-amp has the transfer characteristics of Fig.2.9 (b).

It may be seen that the change in the output state takes place with an increment in input u, of only 2 mV. This is the uncertainty region where output cannot be directly defined. There are basically two types of comparators:

- Non-inverting comparator

- Inverting comparator.

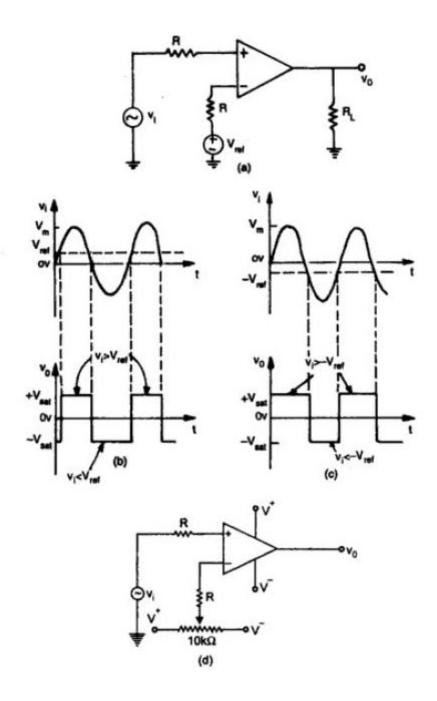

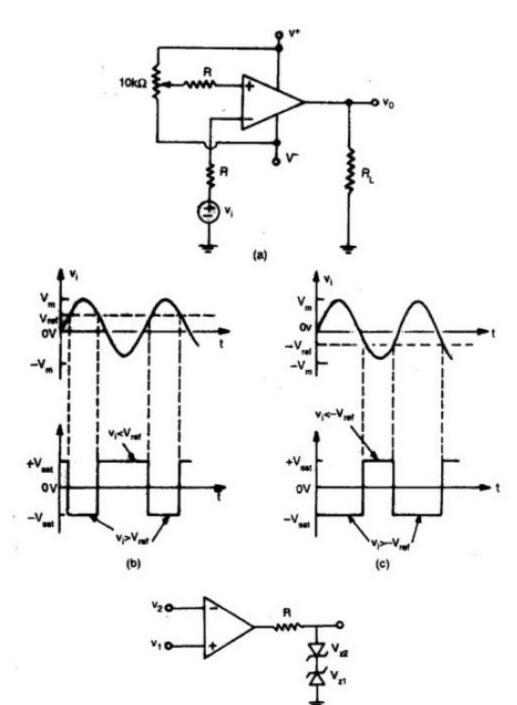

The circuit of Fig.2.10 (a) is called a non-inverting comparator. A fixed reference voltage  $V_{ref}$  is applied to (-) input and a time varying signal  $v_{in}$  is applied to (+) input. The output voltage is at - Vsat for  $v_{in <} v_{ref}$ . The output waveform for a sinusoidal input signal applied to the (+) input is shown in Fig. 2.10 (b and c) for positive and negative Vref respectively.

In a practical circuit Ver is obtained by using a 10 k potentiometer which forms a voltage divider with the supply voltages V+ and V- with the wiper connected to (-) input terminal as shown in Fig.2.10 (d). Thus a Vref of desired amplitude and polarity can be obtained by simply adjusting the 10 k potentiometer.

Figure 2.11 (a) shows a practical inverting comparator in which the reference voltage Vref is applied to the (+) input and u, is applied to (-) input. For a sinusoidal input signal, the output waveform is shown in Fig.2.11 (b) and (c) for  $V_{ref}$  positive and negative respectively.

36

Output voltage levels independent of power supply voltages can also be obtained by using a resistor R and two back to back zener diodes at the output of op-amp as shown in Fig. 2.11 (d).

Figure 2.10

LINEAR AND DIGITAL ICS AND APPLICATIONS

Figure 2.11

# 2.2.5 Schmitt Trigger

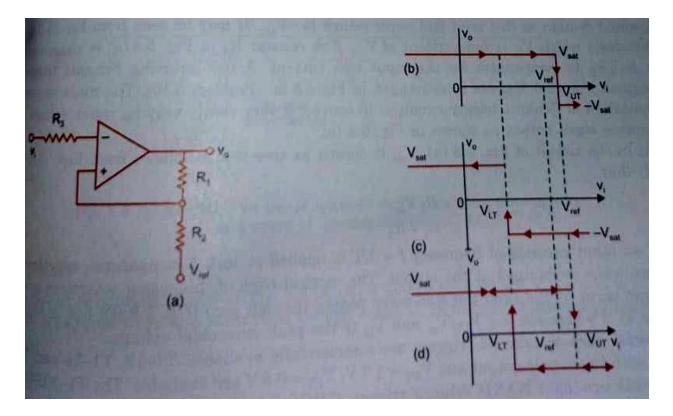

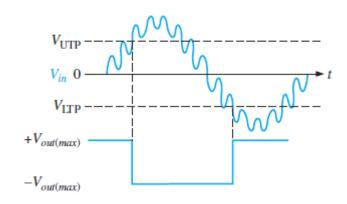

When positive feedback is added to the comparator circuit, gain can be increased greatly. Consequently, the transfer curve of comparator becomes more close to ideal curve. Theoretically, if the loop gain  $-\beta_{AoL}$  is adjusted to unity, then the gain with feedback,  $A_v$ , becomes infinite. This results in an abrupt (zero rise time) transition between the extreme values of output voltage. In practical circuits, however, it may not be possible to maintain loop-gain exactly equal to unity for a long time because of supply voltage and temperature variations. So a value greater than unity is chosen. This also gives an output wave- form virtually discontinuous at the comparison voltage. This circuit, however, now exhibits a phenomenon called hysteresis or backlash.

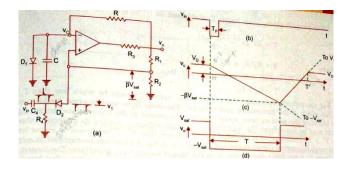

Figure 2.12

Figure 2.12 (a) shows such a regenerative comparator. The circuit is also known as Schmitt Trigger. The input voltage is applied to the (-) input terminal and feedback voltage to the (+) input terminal. The input voltage v triggers the output v, every time it exceeds certain voltage levels. These voltage levels are called upper threshold voltage ( $V_{UT}$ ) and lower threshold voltage ( $V_{LT}$ ). The hysteresis width is the difference between these two threshold voltages. These threshold voltages are calculated as follows.

$$V_{UT} = \frac{v_{ref}R_1}{R_1 + R_2} + \frac{v_{sat}R_2}{R_1 + R_2}$$

This voltage is called upper threshold voltage  $V_{UT}$ . As long as  $v_i$  is less than  $V_{UT}$ , the output  $V_o$ , remains constant at + Vsat. When  $v_i$  is just greater than  $V_{UT}$ , the output regeneratively switches to -Vsat and remains at this level as long as  $v_i > V_{UT}$  as shown in Fig.2.12 (b). For  $v_o = -V$ sat the voltage at the (+) input terminal is,

$$V_{LT} = \frac{v_{ref}R_1}{R_1 + R_2} - \frac{v_{sat}R_2}{R_1 + R_2}$$

This voltage is referred to as lower threshold voltage  $V_{LT}$ . The input voltage  $v_i$  must become lesser than  $V_{LT}$  in order to cause  $v_o$ , to switch from -Vsat to +Vsat. A regenerative transition takes place as shown in Fig.2.12 (c) and the output  $v_o$  returns from -Vsat to +Vsat almost instantaneously. The complete transfer characteristics are shown in Fig.2.12 (d).

Note that the difference between these two voltages is the hysteresis width  $V_H$  and can be written as

$$V_{\rm H} = V_{\rm UT} - V_{\rm LT}$$

Figure 2.12(e) show the CRO output for the schmitt trigger

figure 2.12(e)

# 2.2.6 Multivibrators and Waveform generators

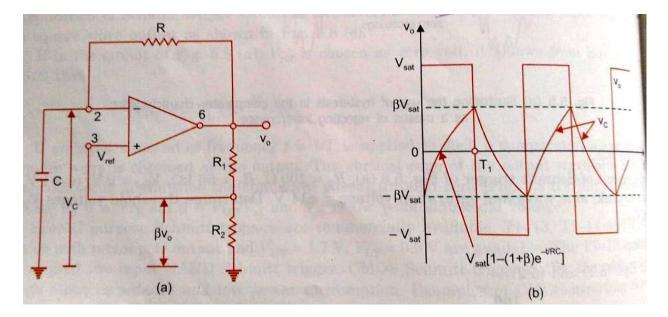

## Astable Multivibrators [ square wave generators]

A simple op-amp square wave generator is shown in Fig. 2.13 (a). Also called a free running oscillator, the principle of generation of square wave output is to force an op-amp to operate in the saturation region. In Fig.2.13 (a) fraction  $\beta = R2/(R1 + R2)$  of the output is fedback to the (+) input terminal. Thus the reference voltage Vref is  $V_o$ , and may take values  $+\beta V_{sat}$  or  $-\beta V_{sat}$ .

Figure 2.13

LINEAR AND DIGITAL ICS AND APPLICATIONS

The output is also fed back to the (-) input terminal after integrating by means of a low-pass RC combination. Whenever input at the (-) input terminal just exceeds Vref switching takes place resulting in a square wave output. In astable multivibrator, both the states are quasi stable. The capacitor now starts charging

Consider an instant of time when the output is at +Vsat towards-Vsat through-resistance R, as shown in Fig. 2.13 (b). The voltage at the (+) input terminal is held at +  $\beta$ V <sub>sat</sub> by R, and RC, combination. This condition continues as the charge on C rises, until it has just exceeded +  $\beta$ V <sub>sat</sub> the reference voltage. When the voltage at the (-) input terminal becomes just greater than this reference voltage, the output is driven to At this instant, the voltage on the capacitor is +  $\beta$ V <sub>sat</sub>. It begins to discharge through R. that is, charges toward –Vsat. When the output voltage switches to –Vsat the capacitor charges more and more negatively until its voltage just exceeds -  $\beta$ V <sub>sat</sub>. The output switches back to + V. The cycle repeats itself as shown in Fig.2.13 (b). The frequency is determined by the time it takes the capacitor to charge from -  $\beta$ V <sub>sat</sub> to +Vsat and vice versa. The voltage across the capacitor as a function of time is given by,

v(t) = Vf + (Vi-Vf)exp(-t/RC)

Vf = +Vsat

$V_i = -\beta V_{sat}$

When  $t=T_1$ ,

$T_1 = RC \frac{1+\beta}{1-\beta}$

$T=2 T_1 = 2 RC \frac{1+\beta}{1-\beta}$

When  $\beta = 1/2$ , we get

T = 2.2 RC

#### MONOSTABLE MULTIVIBRATOR

Monostable multivibrator has one stable state and the other is quasi stable state, the is useful for generating single output pulse of adjustable time duration in response to triggering signal. The width of the output pulse depends only on external components connected to the op-amp. The circuit shown in Fig. 2.14(a) is a modified form of the astable multivibrator. A diode D1 clamps the capacitor voltage to 0.7 V when the output is at +VA negative going pulse signal of magnitude V1 passing through the differentiator RC, and diode L produces a negative going triggering impulse and is applied to the (+) input terminal. To analyze the circuit, let us assume that in the stable state, the output Vo, is at +Vsat and diode D1 conducts and v, the voltage across the capacitor C gets clamped to +0.7 V. The voltage at the (+) input terminal through  $R_1 R_2$  potentiometric divider is +  $\beta V_{sat}$  Now, negative trigger of magnitude V, is applied to the (+) input terminal so that the effective signal at this terminal is less than 0.7 V, i.e. ([ $\beta$  Vsat+(-V1)]< 0.7 V), the output of the op amp will switch from + V<sub>sat</sub> to - V<sub>sat</sub> .The diode will now get reverse biased and the capacitor starts charging exponentially to -Vsat through the resistance R. The voltage at the (+) input terminal is now -  $\beta$  V<sub>sat</sub>. When the capacitor voltage v, becomes just slightly more negative the output of the op-amp switches back to  $+ V_{sat}$ . The capacitor C now starts charging to + V<sub>sat</sub> through R until v, is 0.7V as capacitor C gets clamped to the voltage .The pulse width T of monostable multivibrator is calculated as follows:

The general solution for a single time constant low pass RC circuit with V, and V, as initial and final values is,

v(t) = Vf + (Vi-Vf)exp(-t/RC) Vf = -V sat  $Vi = V_D$  At t = T  $T = RC \ln \frac{(1+Vd+V \text{ sat})}{1-\beta}$   $When \beta = \frac{R_1}{R_1+R_2} = 0.5$  T = 0.69 RC

For monostable operation, the trigger pulse width should be much less than the T. pulse width of the monostable multivibrator. The diode D is used to avoid malfunctioning by blocking the positive noise spikes that may be present at the differentiated trigger input It may be noted from Fig. 2.14 (b) that capacitor voltage u, reaches its quiescent value V at T. Therefore, it is essential that a recovery time T.T be allowed to elapse before the next triggering signal is applied. The circuit of Fig. 2.14 (a) can be modified to achieve voltage to time delay conversion as in the case of square wave generators. The monostable multivibrator circuit is also referred to as time delay circuit as it generates a fast transition at a predetermined time T after the application of input trigger. It is also called a gating circuit as it generates a rectangular waveform at a definite time and thus could be used gate parts of a system.

Figure 2.14

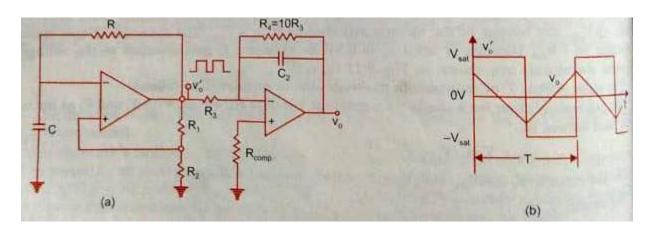

## TRIANGULAR WAVE GENERATOR

A triangular wave can be simply obtained by integrating a square wave as shown in Fig 2.15 (a). It is obvious that the frequency of the square wave and triangular wave is the same as shown in Fig.2.15 (b). Although the amplitude of the square wave is constant at V the amplitude of the triangular wave will decrease as the frequency increases. This because the reactance of the capacitor C, in the feedback circuit decreases at high frequencies A resistance R, is connected across C, to avoid the saturation problem at low frequencies as in the case of practical integrator.

Figure 2.15

# UNIT-III ACTIVE FILTERS, TIMERS AND PHASE LOCKED LOOPS

ACTIVE FILTERS: Introduction, Butterworth filters  $-1^{st}$  order,  $2^{nd}$  order low pass and high pass filters, band pass, band reject and all pass filters.

TIMER AND PHASE LOCKED LOOPS: Introduction to IC 555 timer, description of functional diagram, monostable and astable operations and applications, Schmitt trigger, PLL - introduction, basic principle, phase detector/comparator, voltage controlled oscillator (IC 566), low pass filter, monolithic PLL and applications of PLL

## **3.1 Active Filters**

## **3.1.1 Introduction**

Filters are circuits that are capable of passing signals with certain selected frequencies while rejecting signals with other frequencies. This property is called *selectivity*. Active filters use transistors or op-amps combined with passive *RC*, *RL*, or *RLC* circuits. The active devices provide voltage gain, and the passive circuits provide frequency selectivity. Although inductors are used in passive filters, they are avoided in active filters because inductors tend to be bulky, more expensive than capacitors, and not easily integrated. In terms of general response, the four basic categories of active filters are low-pass, high-pass, band-pass, and band-stop. In this chapter, you will study active filters using op-amps and *RC* circuits.

## **3.1.2 Butterworth Characteristics:**

The **Butterworth** characteristic provides a very flat amplitude response in the passband and a roll-off rate of -20 dB/decade/pole. The phase response is not linear, however, and the phase shift (thus, time delay) of signals passing through the filter varies nonlinearly with frequency. Therefore, a pulse applied to a filter with a Butterworth response will cause overshoots on the output because each frequency component of the pulse's rising and falling edges experiences a different time delay. Filters with the Butterworth response are normally used when all frequencies in the pass band must have the same gain. The Butterworth response is often referred to as a maximally flat response.

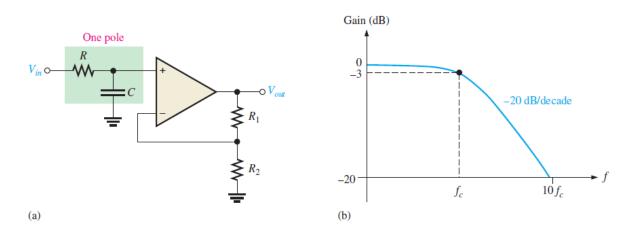

## 3.1.3 Active low pass filters

# 1<sup>st</sup> Order low pass filter:

Figure 3.1(a) shows an active filter with a single low-pass *RC* frequency-selective circuit that provides a roll-off of -20 dB/decade above the critical frequency, as indicated by the response curve in Figure 3.1(b). The critical frequency of the single-pole filter is  $f_c = 1/(2\pi RC)$ .

Figure 3.1

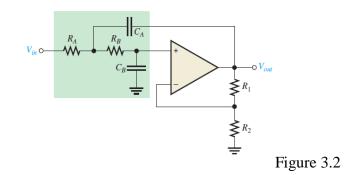

# 2<sup>nd</sup> Order low pass filter:

The Sallen-Key is one of the most common configurations for a second-order (two-pole) filter. It is also known as a VCVS (voltage-controlled voltage source) filter. A low-pass version of the Sallen-Key filter is shown in Figure 3.2. Notice that there are two lowpass *RC* circuits that provide a roll-off of -40 dB/decade above the critical frequency (assuming a Butterworth characteristic). One *RC* circuit consists of  $R_A$  and  $C_A$ , and the second circuit consists of  $R_B$  and  $C_B$ . A unique feature of the Sallen-Key low-pass filter is the capacitor *CA* that provides feedback for shaping the response near the edge of the pass band. The critical frequency for the Sallen-Key filter is

$$f_{

m c} rac{1}{\sqrt{2\pi R_A R_B C_A C_B}}$$

## Higher order Low pass filters

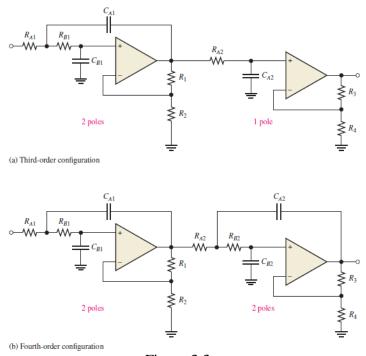

A three-pole filter is required to get a third-order low-pass response (-60 dB/decade). This is done by cascading a two-pole Sallen-Key low-pass filter and a single-pole lowpass filter, as shown in Figure 3.3(a). Figure 3.3(b) shows a four-pole configuration obtained by cascading two Sallen-Key (two-pole) low-pass filters. In general, a four-pole filter is preferred because it uses the same number of op-amps to achieve a faster roll-off.

Figure 3.3

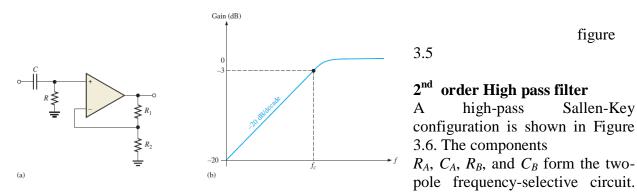

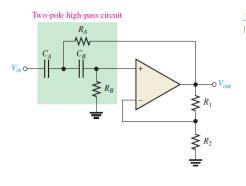

# 3.1.4 Active High pass filters

# 1<sup>st</sup> order High pass filter

A high-pass active filter with a -20 dB/decade roll-off is shown in Figure 3.4(a). Notice

that the input circuit is a single high-pass *RC* circuit. The negative feedback circuit is the same as for the low-pass filters previously discussed. The high-pass response curve is shown in Figure 3.4(b).

Notice that the positions

of the resistors and capacitors in the frequency-selective circuit are opposite to those in the low-pass configuration. As with the other filters, the response characteristic can be optimized by proper selection of the feedback resistors, R1 and R2.

Figure 3.6

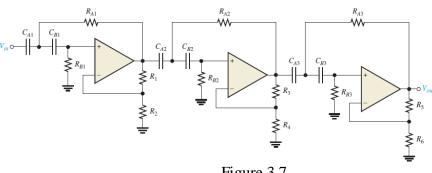

## Higher order High pass Filter

As with the low-pass configuration, first- and second-order high-pass filters can be cascaded to provide three or more poles and thereby create faster roll-off rates. Figure 3.7 shows a six-pole high-pass filter consisting of three Sallen-Key two-pole stages. With this configuration optimized for a Butterworth response, a roll-off of -120 dB/decade is achieved.

Figure 3.7

#### 3.1.5 Active Band pass filter

#### **Cascading of High Pass and Low Pass Filters**

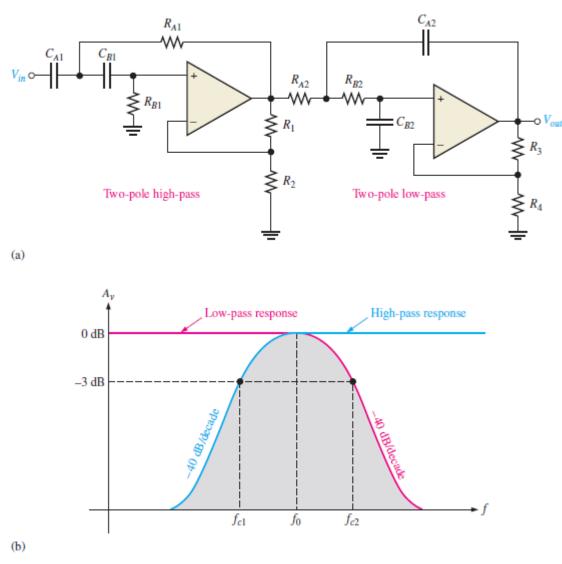

One way to implement a band-pass filter is a cascaded arrangement of a high-pass filter and a low-pass filter, as shown in Figure 3.8(a), as long as the critical frequencies are sufficiently separated. Each of the filters shown is a Sallen-Key Butterworth configuration so that the roll-off rates are -40 dB/decade, indicated in the composite response curve of Figure 3.8(b). The critical frequency of each filter is chosen so that the response curves overlap sufficiently, as indicated. The critical frequency of the high-pass filter must be sufficiently lower than that of the low-pass stage. This filter is generally limited to wide bandwidth applications. The lower frequency fc1 of the passband is the critical frequency of the high-pass filter. The upper frequency  $fc^2$  is the critical frequency of the low-pass filter. Ideally, as discussed earlier, the center frequency f0 of the passband is the geometric mean of fc1 and fc2.

$$f_{c1} = \frac{1}{\sqrt{2\pi R_A R_B C_A C_B}}$$

$$f_{c2} = \frac{1}{\sqrt{2\pi R_A R_B C_A C_B}}$$

$$f_0 = \sqrt{f c 1 f c 2}$$

LINEAR AND DIGITAL ICs AND APPLICATIONS

Figure 3.8

#### **3.1.6 Band Stop Filter**

#### **Multiple Feedback Band Stop filter**

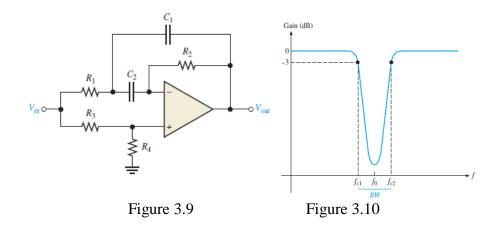

Another category of active filter is the **band-stop filter**, shown in Figure 3.9 also known as *notch*, *band-reject*, or *band-elimination* filter. You can think of the operation as opposite to that of the bandpass filter because frequencies within a certain bandwidth are rejected, and frequencies outside the bandwidth are passed. A general response curve for a band-

stop filter is shown in Figure 3.10. Notice that the bandwidth is the band of frequencies between the 3 dB points, just as in the case of the band-pass filter response.

#### 3.2 Timers

## 3.2.1 Introduction to IC 555 timer

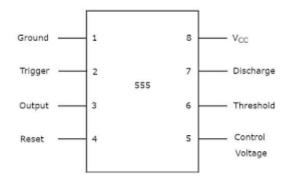

The 555 timer is a highly stable device for generating accurate time delay or oscillation, Signetics Corporation first introduced this device as the SE555/NE555 and it is available in two package styles, 8-pin circular style, TO-99 can or 8-pin mini DIP or as 14-pin DIP. The 556 timer contains two 555 timers and is a 14-pin DIP. There is also available counter timer such as Exar's XR-2240 which contains a 555 timer plus a programmable binary counter in a single 16-pin package A single 555 timer can provide time delay ranging from microseconds to hours whereas counter timer can have a maximum timing range of days.

The 555 timer can be used with supply voltage in the range of +5V to +18V and can drive load upto 200 mA. It is compatible with both TTL and CMOS 7 logic circuits. Because of the wide range of supply voltage, the 555 timer is versatile and easy to use in various applications. Various applications include oscillator, pulse generator, ramp and square wave generator, monoshot multivibrator, burglar, alarm, traffic light control and voltage monitor etc.

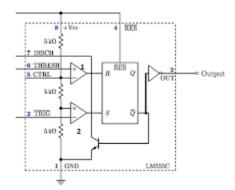

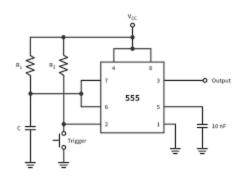

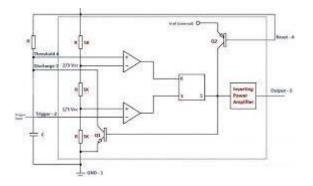

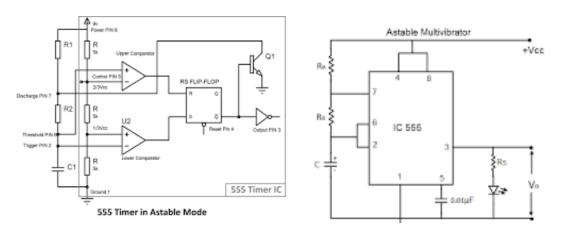

#### **3.2.2 DESCRIPTION OF FUNCTIONAL DIAGRAM**

Figure 3.11 gives the pin diagram and Fig. 3.12 gives the functional diagram for 555 IC timer. Referring to Fig.3.11, three 5 k $\Omega$  internal resistors act as voltage divider, providing bias voltage of (2/3) Vcc to the upper comparator (UC) and (1/3) Vcc to the lower comparator (LC), where Vec is the supply voltage. Since these two voltages fix the necessary comparator threshold voltage, they also aid in determining the timing interval. It is possible to vary time electronically too, by applying a modulation voltage to the control voltage input terminal (pin 5). In applications, where no such modulation is intended, it is recommended by manufacturers that a capacitor (0.01  $\mu$ F) be connected between control voltage terminal (pin 5) and ground to by-pass noise or ripple from the supply.

Figure 3.12

In the standby (stable) state, the output  $\underline{Q}$  of the control flip-flop (FF) is HIGH. This makes the output LOW because of the power amplifier which is basically an inverter. A negative going trigger pulse is applied to pin 2 and should have its dc level greater than the threshold level of the lower comparator (i.e. Vcc/3). At the negative going edge of the trigger, as the trigger passes through (Vcc/3), the output of the lower comparator goes HIGH and sets the FF (Q= 1,  $\underline{Q}$ = 0). During the positive excursion, when the threshold voltage at pin 6 passes through (2/3) Vcc, the output of the upper comparator goes HIGH and resets the FF ( $\underline{Q}$ = 1, Q = 0). The reset input (pin 4) provides a mechanism to reset the FF in a manner which overrides the effect of any instruction coming to FF from the lower comparator. This overriding reset is effective when the reset input is less than about 0.4 V. When this reset is not used, it is returned to Vcc. The transistor Q2 is driven by an internal reference voltage Vref obtained from supply voltage Vcc.

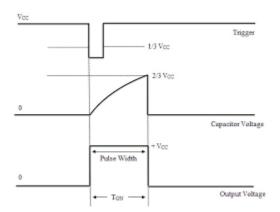

#### **3.2.3 Monostable Operation**

Figure 3.13 shows a 555 timer connected for monostable operation and its functional diagram is shown in Fig.3.14. In the standby state, FF holds transistor Q, on, thus clamping the external timing capacitor C to ground. The output remains at ground potential, i.e. LOW. As the trigger passes through Vcc/3, the FF is set, i.e. Q = 0. This makes the transistor Q1 off and the short circuit across the timing capacitor C is released. As Q1 is LOW, output goes HIGH (= Vcc). The timing cycle now begins. Since C is unclamped, voltage across it rises exponentially through R towards Vcc with a time constant RC as in Fig.3.15(b). After a time period T (calculated later), the capacitor voltage is just greater than (2/3) Vcc and the upper comparator resets the FF, that is, R = 1, S = 0 (assuming very small trigger pulse width). This makes Q = 1, transistor Q1 goes on (i.e. saturates), thereby discharging the capacitor C rapidly to ground potential. The output returns to the standby state or ground potential as shown in Fig. 3.15 (c).

Figure 3.14

Figure 3.15

## **Applications of Monostable Operations**

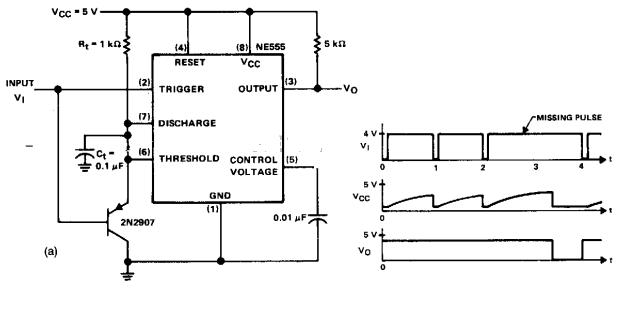

#### **Missing Pulse Detector**

Figure 3.16 (a)

Missing pulse detector circuit using 555 timer is shown in Fig.3.16(a). Whenever, input trigger is low, the emitter diode of the transistor Q is forward biased. The capacitor C gets clamped to few tenths of a volt (~ 0.7 V). The output of the timer goes HIGH. The circuit is designed so that the time period of the monostable circuit is slightly greater (1/3 longer) than that of the triggering pulses. So long the trigger pulse train keeps coming at pin 2, the output remains HIGH. However, if a pulse misses, the trigger input is high and transistor Q is cutoff. The 555 timer enters into normal state of monostable operation. The output goes LOW after time T of the mono-shot. Thus this type of circuit can be used to detect missing heartbeat. It can also be used for speed control and measurement. If input trigger pulses are generated from a rotating wheel, the circuit tells when the wheel speed drops below a predetermined value.

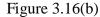

## **Frequency Divider**

A continuously triggered monostable circuit when triggered by a square wave generator can be used as a frequency divider, if the timing interval is adjusted to be longer than the period of the triggering square wave input signal. The monostable multivibrator will be triggered by the first negative going edge of the square wave input but the output will remain HIGH (because of greater timing interval) for next negative going edge of the input square wave as shown in Fig.3.17. The mono-shot will however be triggered on the third negative going input, depending on the choice of the time delay. In this way, the output can be made integral fractions of the frequency of the input triggering square wave.

Figure 3.17

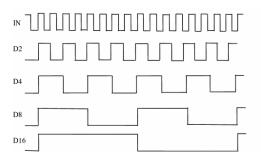

#### **Pulse Width Modulation**

The circuit is shown in Fig.3.18. This is basically a monostable multivibrator with a modulating input signal applied at pin-5. By the application of a continuous trigger at pin-2, a series of output pulses are obtained. the duration of which depends on the modulating input at pin-5. The modulating signal applied at pin-5 gets superimposed upon the already existing voltage (2/3) Vec the inverting input terminal of UC. This in turn changes the threshold level of UC and the output pulse width modulation takes place. The modulating signal and the output waveform are shown in Fig. 3.18. It may be noted from the output waveform that the pulse duration, that is, the duty cycle only varies, keeping the frequency same as that of the continuous input pulse at train trigger.

#### **3.2.4 Astable Operation**

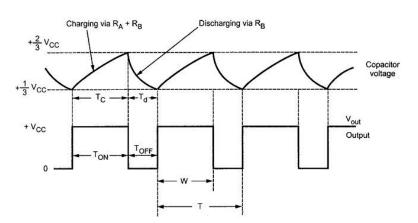

The device is connected for astable operation as shown in Fig.3.19. For better understanding, the complete diagram of astable multivibrator with a detailed internal diagram of 555 is shown in Fig.3.19. Compared with monostable operation, the timing resistor is now split into two sections R and RB. Pin 7 of discharging transistor Q, is connected to the junction of  $R_A$  and  $R_B$ . When the power supply Vcc is connected, the external timing capacitor C charges towards Vcc with a time constant ( $R_A + R_B$ )C. During this time, output (pin 3) is high (equals Vcc) as Reset R = 0, Set S = 1 and this combination makes  $\underline{Q} = 0$  which has unclamped the timing capacitor C.

When the capacitor voltage equals (to be precise is just greater than), (2/3) Vcc the upper comparator triggers the control flip-flop so that  $\underline{Q}$ =1. This, in turn, makes transistor Q, on and capacitor C starts discharging towards ground through R<sub>B</sub> and transistor Q, with a time constant R<sub>B</sub>C(neglecting the forward resistance of Q1). Current also flows into transistor Q through R. Resistors R<sub>A</sub> and R<sub>B</sub> must be large enough to limit this current and prevent damage to the discharge transistor Q1. The minimum value of R<sub>A</sub> is approximately equal to Vcc/0.2 where 0.2 A is the maximum current through the on transistor Q. During the discharge of the timing capacitor C, as it reaches (to be precise, is just less than) Vcc/3, the lower comparator is triggered

58

and at this stage S = 1, R = 0, which turns  $\underline{Q}$ = 0. Now  $\underline{Q}$  = 0 unclamps the external timing capacitor C. The capacitor C is thus periodically charged and discharged between (2/3) Vcc and (1/3) Vcc respectively. Figure 3.20 shows the timing sequence and capacitor voltage wave form. The length of time that the output remains HIGH is the time for the capacitor to charge from (1/3) Vcc to (2/3) Vcc.

Figure 3.20

## **Applications of Astable Operation**

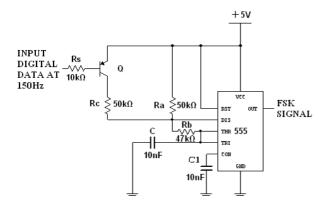

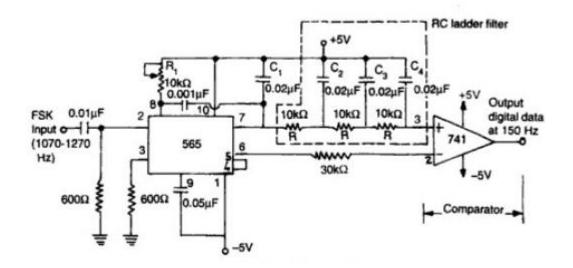

## **Frequency Shift Keying Generator**

figure 3.21

In digital data communication, binary code is transmitted by shifting a carrier frequency between two preset frequencies. This type of transmission is called frequency shift keying (FSK) technique. A 555 timer in astable mode can be used to generate FSK signal. The circuit is as shown in Fig.3.21. The standard digital data input frequency is 150 Hz. When input is HIGH, transistor Q is off and 555 timer works in the normal astable mode of operation. The frequency of the output waveform given by Eq. (9.1) can be rewritten as

## $f_o = 1.45/(R_A + 2R_B)C$

In a tele-typewriter using a modulator-demodulator (MODEM), a frequency between 1070 Hz to 1270 Hz is used as one of the standard FSK signals. The components  $R_A$  and  $R_B$  and the capacitor C can be selected so that  $f_o$  is 1070 Hz. When the input is LOW, Q goes on and connects the resistance  $R_C$  across  $R_A$ . The output frequency is now given by

$$f_o = 1.45/(R_A || R_C) + 2R_B$$

The resistance  $R_C$  can be adjusted to get an output frequency 1270 Hz.

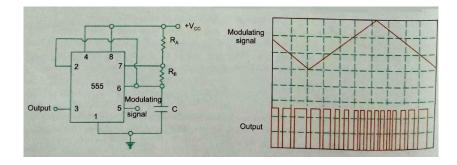

#### **Pulse Position Modulator**

Figure 3.22

The pulse-position modulator can be constructed by applying a modulating signal to pin 5 of a 555 timer connected for astable operation as shown in Fig. 3.22. The output pulse position varies with the modulating signal, since the threshold voltage and hence the time delay is varied. Figure 9.23 shows the output waveform generated for a triangle wave modulation signal. It may be noted from the output waveform that the frequency is varying leading to pulse position modulation. The typical practical component values may be noted as

$R_A = 3.9 \text{ k}\Omega, R_B = 3 \text{ k}\Omega, C = 0.01 \mu\text{F}$

Vcc = 5 V (any value between 5 V to 18 V may be chosen)

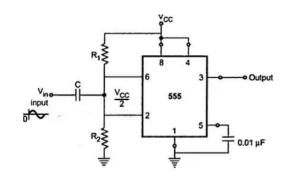

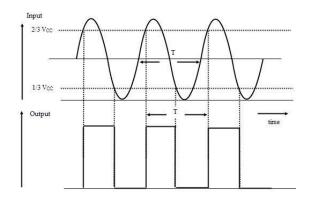

## 3.2.4 Schmitt Trigger

The use of 555 timer as a Schmitt Trigger is shown in Fig. 3.23. Here the two internal comparators are tied together and externally biased at Vcc/2 through R1 and R2. Since the upper comparator will trip at (2/3) Vcc and lower comparator at (1/3) Vcc, the bias provided by R1 and R2 is centered within these two thresholds. Thus, a sine wave of sufficient amplitude (> Vcc/6 = 2/3 Vcc - Vcc/2) to exceed the reference levels causes the internal flip-flop to alternately set and reset, providing a square wave output as shown in Fig. 3.24.

61

Figure 3.23

Figure 3.24

## **3.3 Phase Locked Loops**

## **3.3.1 Introduction**

The phase-locked loop (PLL) is an important building block of linear systems. Electronic phaselocked loop (PLL) came into vogue in the 1930s when it was used for radar synchronisation and communication applications. The high cost of realising PLL in discrete form limited its use earlier. Now with the advanced IC technology, PLLs are available as inexpensive monolithic ICs. This technique for electronic frequency control is used today in satellite communication systems, air borne navigational systems, FM communication systems, computers etc. The basic principle of PLL, different ICs and important applications are discussed.

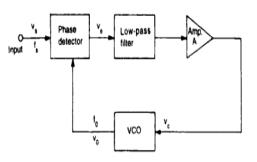

## 3.3.2 Basic Principles Of PLL

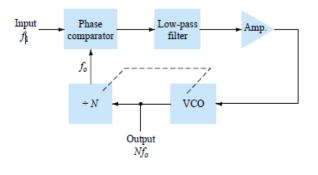

The basic block schematic of the PLL is shown in Fig.3.25. This feedback system consists of:

- 1. Phase detector/comparator

- 2. A low pass filter

- 3. An error amplifier

- 4. A Voltage Controlled Oscillator (VCO)

The VCO is a free running multivibrator and operates at a set frequency  $f_0$  called free running frequency. This frequency is deter- mined by an external timing capacitor and an external resistor. It can also be shifted to either side by applying a de control voltage v, to an appropriate terminal of the IC. The frequency deviation is directly proportional to the de control voltage and hence it is called a "Voltage Controlled Oscillator" or, in short, VCO.

If an input signal  $v_s$  of frequency  $f_s$  is applied to the PLL, the phase detector compares the phase and frequency of the incoming signal to that of the output  $v_o$  of the VCO. If the two signals differ in frequency and/or phase, an error voltage  $v_e$  is generated. The phase detector is basically a multiplier and produces the sum  $(f_s+f_o)$  and difference  $(f_s-f_o)$  components at its output. The high frequency component  $(f_s+f_o)$  is removed by the low pass filter and the difference frequency component is amplified and then applied as control voltage v to VCO. The signal v, shifts the VCO frequency in a direction to reduce the frequency difference between f, and fo. Once this action starts, we say that the signal is in the capture range. The VCO continues to change frequency till its output frequency is exactly the same as the input signal frequency. The circuit is then said to be locked. Once locked, the output frequency f, of VCO is identical to f, except for a finite phase difference . This phase difference generates a corrective control voltage v, to shift the VCO frequency from f, to f, and thereby maintain the lock. Once locked, PLL tracks the frequency changes of the input signal. Thus, a PLL goes through three stages (i) free running, (ii) capture and (iii) locked or tracking.

LINEAR AND DIGITAL ICS AND APPLICATIONS

Figure 3.25

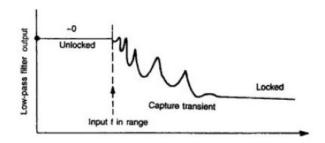

Figure 3.26 shows the capture transient. As capture starts, a small sine wave appears. This is due to the difference frequency between the VCO and the input signal. The de component of the beat drives the VCO towards the lock. Each successive cycle causes the VCO frequency to move closer to the input signal frequency. The difference in frequency becomes smaller and a large component is passed by the filter, shifting the VCO frequency further. The process continues until the VCO locks on to the signal and the difference frequency is dc.

The low pass filter controls the capture range. If VCO frequency is far away, the beat frequency will be too high to pass through the filter and the PLL will not respond. We say that the signal is out of the capture band. However, once locked, the filter no longer restricts the PLL. The VCO can track the signal well beyond the capture band. Thus tracking range is always larger than the capture range.

Figure 3.26

Some of the important definitions in relation to PLL are:

Lock-in Range: Once the PLL is locked, it can track frequency changes in the incoming signals. The range of frequencies over which the PLL can maintain lock with the incoming signal is called the lock- in range or tracking range. The lock range is usually expressed as a percentage of  $f_0$ , the VCO frequency.

Capture Range: The range of frequencies over which the PLL can acquire lock with an input signal is called the capture range. This parameter is also expressed as percentage of  $f_o$

Pull-in time: The total time taken by the PLL to establish lock is called pull-in time. This depends on the initial phase and frequency difference between the two signals as well as on the overall loop gain and loop filter characteristics.

#### **3.3.3 Phase Detector/Comparator**

The phase detection is the most important part of the PLL system. There are two types of phase detectors used, analog and digital.

## **Analog Phase Detector**

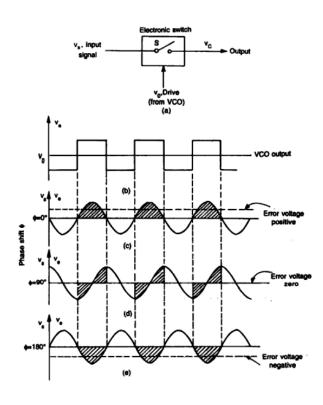

The principle of analog phase detection using switch type phase detector is shown in Fig. 3.27(a). An electronic switch S is opened and closed by signal coming from VCO (normally a square wave) as shown in Fig. 3.27(b). The input signal is, therefore, chopped at a repetition rate determined by VCO frequency. Figure 3.27(c) shows the input signal v, assumed to be in phase (=  $0^{\circ}$ ) with VCO output v. Since the switch S is closed only when VCO output is positive, the output waveform v will be half sinusoids (shown hatched). Similarly, the output waveform for =  $90^{\circ}$  and  $180^{\circ}$  is shown in Fig. 3.27(d, e). This type of phase detector is called a half wave detector, since the phase information for only one-half of the input waveform is detected and averaged. The output of the phase comparator when filtered through a low pass filter gives an error signal which is the average value of the output waveform shown by dotted line in Fig.

3.27(c, d, e). It may be seen that the error voltage is zero when the phase shift between the two inputs is 90°. So, for perfect lock, the VCO output should be 90° out of phase with respect to the input signal.

Figure 3.27

#### **Digital Phase Detector**

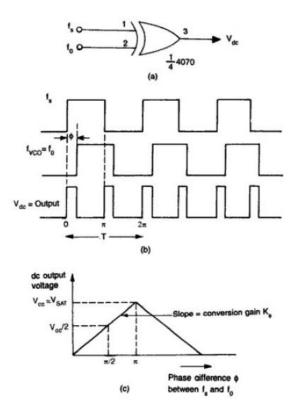

Figure 3.28(a) shows the digital type XOR (Exclusive-OR) phase detector. It uses CMOS type 4070 Quad 2-input XOR gate. The output of the XOR gate is high when only one of the inputs signals  $f_s$  or  $f_o$  is high. This type of detector is used when both the input signals are square waves. The input and output waveforms for  $f_s = f_o$ . are shown in Fig. 3.28(b). In this figure,  $f_s$  is leading  $f_o$  by  $\varphi$  degrees. The variation of dc output voltage with phase difference  $\varphi$  is shown in Fig. 3.28(c). It can be seen that the maximum de output voltage occurs when the phase difference  $\pi$  is a because the output of the gate remains high throughout. The slope of the curve gives the conversion ratio k  $_{\varphi}$  of the phase detector. So, the conversion ratio K  $_{\varphi}$  for a supply voltage Vcc = 5V is,

66

$$K_{\phi} = \frac{5}{\pi} = 1.59 \text{ V/rad}$$

Figure 3.28

#### 3.3.4 Voltage Controlled Oscillator

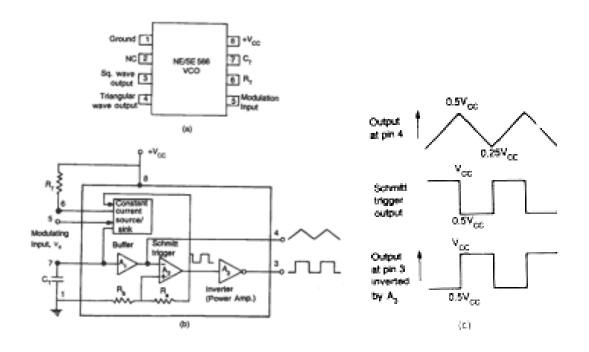

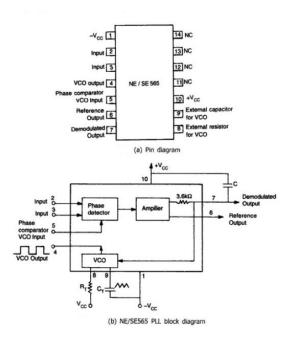

A common type of VCO available in IC form is Signetics NE/SE566. The pin configuration and basic block diagram of 566 VCO are shown in Fig.3.29(a, b). Referring to Fig. 3.29(b), a timing capacitor  $C_T$  is linearly charged or discharged by a constant current source/sink. The amount of current can be controlled by changing the voltage  $v_c$  applied at the modulating input (pin 5) or by changing the timing resistor  $R_T$  external to the IC chip. The voltage at pin 6 is held at the same voltage as pin 5. Thus, if the modulating voltage at pin 5 is increased, the voltage at pin 6 also increases, resulting in less voltage across  $R_T$  and thereby decreasing the charging current.

The voltage across the capacitor  $C_T$  is applied to the inverting input terminal of Schmitt trigger  $A_1$  via buffer amplifier  $A_2$ . The output voltage swing of the Schmitt trigger is designed to Vcc

67

and 0.5 V If  $R_a=R_b$  in the positive feedback loop, the voltage at the non-inverting input terminal of A, swings from 0.5 V to 0.25 Vee In Fig. 3.29(c). when the voltage on the capacitor  $C_T$ exceeds 0.5 Vcc during charging, the output of the Schmitt trigger goes LOW (0.5 Vcc). The capacitor now discharges and when it is at 0.25 Vcc, the output of Schmitt trigger goes HIGH (Vcc). Since the source and sink currents are equal, capacitor charges and discharges for the same amount of time. This gives a triangular voltage waveform across  $C_T$  which is also available at pin 4. The square wave output of the Schmitt trigger is inverted by inverter A<sub>3</sub> and is available at pin 3. The output waveforms are shown in Fig. 3.29(c).

$$f_o = \frac{2(V_{cc-V_c})}{R_T C_T V_{cc}}$$

if  $v_c = 7/8Vcc$ , then  $f_o$ ,

$$f_o = \frac{2(V_{cc-7/8V_{cc}})}{R_T C_T V_{cc}}$$

$$f_o = \frac{1}{4R_T C_T}$$

$$f_o = \frac{0.25}{R_T C_T}$$

Figure 3.29

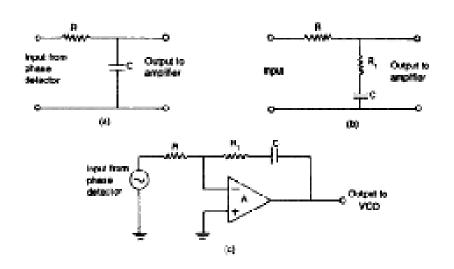

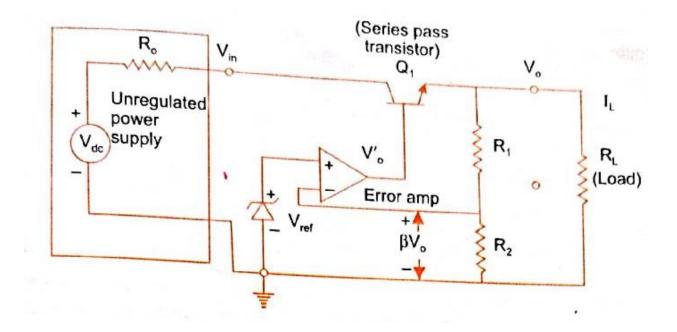

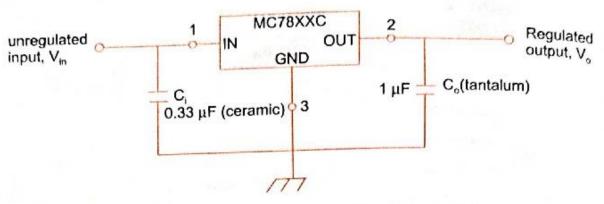

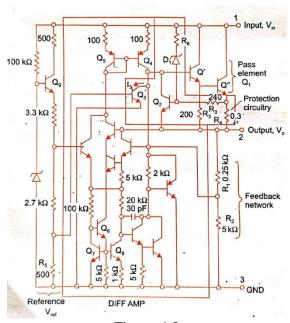

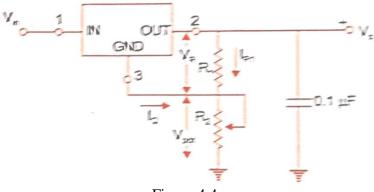

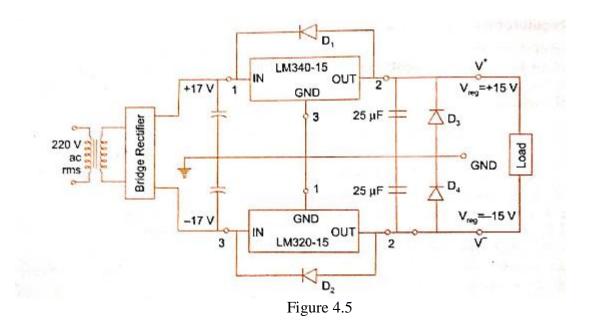

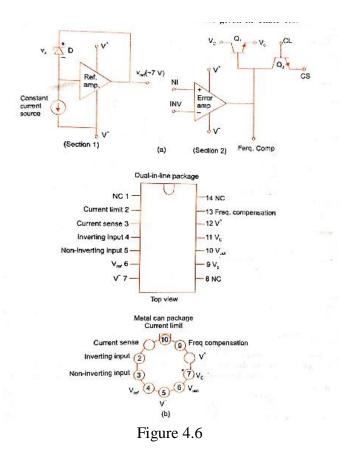

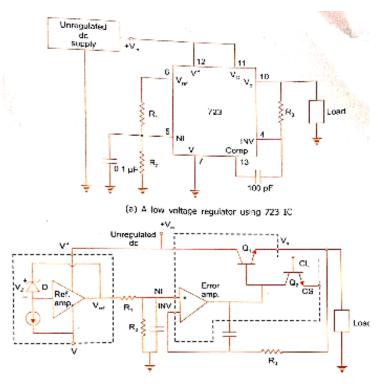

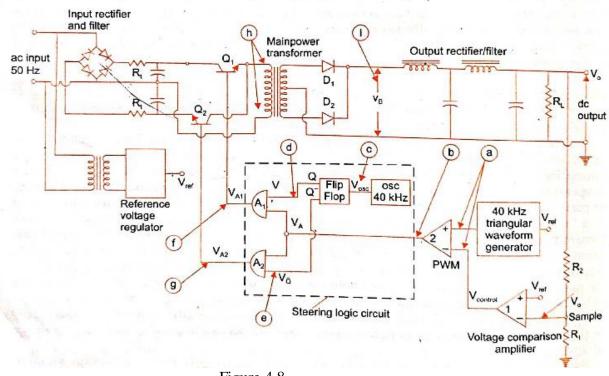

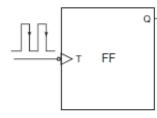

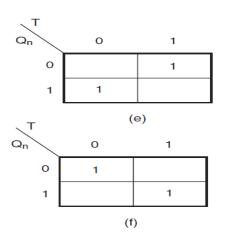

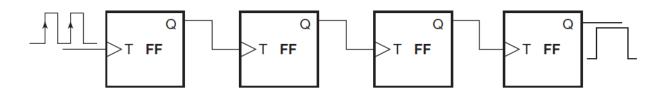

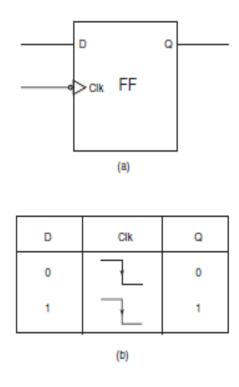

#### 3.3.5 Low Pass Filter